|

《Verilog HDL数字系统设计》

《自动售货机的设计与仿真》

课程设计说明书

仿真波形及分析

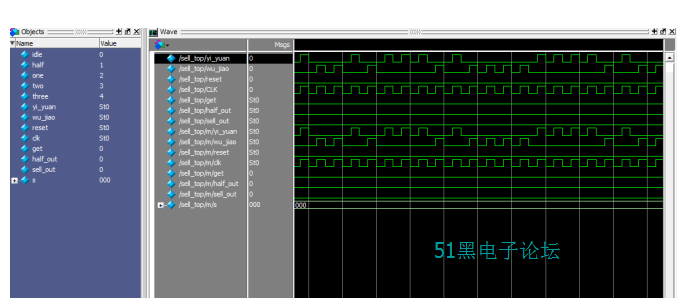

分析前仿真波形,每个时钟周期为 100ns,如图:在100ns 系统复位,到550ns时,输入5个wu_jiao信号, get和sell_out信号出现告电平,

持续100ns,表示卖出和取饮料信号。第三组开始输入信号:在 1050ns且为上升沿时,1 个 yi_yuan 高电平,后接着俩 wu_jiao 高电平,又

一个 yi_yuan 高电平,half_out/get 和 sell_out 信号出现告电平持续100ns,表示分别有卖出、找零和取饮料信号。在1850ns时第5 组测试数据开始,同时为时钟上升沿,分别有三个 wu_jiao和一个yi_yuan高电平,满足输出,get、sell_out 同时为高,持续 100ns,表示分别卖出和取饮料信号。

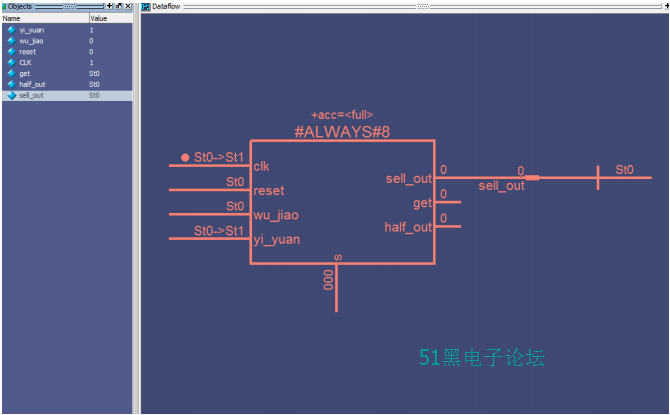

系统的顶层原理图如下:

1.本次仿真实验通过对自动售货机状态转换图的分析得出其工作原理,并根据工作原理编写出Verilog HDL源程序;

2.通过仿真验证,该设计能较好的实现自动售货机的基本功能;

3.根据仿真结果,仿真输出与理论值相比有一定的延时,这是系统误差,难以消除。

三、程序说明

电路变量分析

根据设计要求,共有七个变量。

clk:时钟输入;

reset:系统复位信号;

wu_jiao:代表投入五角硬币;

yi_yuan:代表投入一元硬币;

half_out:售货机找回一枚五角硬币信号;

sell_out:机器售出一瓶饮料;

get:提示投币者取走饮料。

四、知识点说明

1、从仿真的角度来说,HDL语言面对的是编译器(如Modelsim等),相当于软件思路。 这时:

wire对应于连续赋值,如 assign

reg 对应于过程赋值,如 always,initial

从综合的角度来说,HDL 语言面对的是综合器(如 DC 等),要从电路的角度来考虑。 这时:

1、 wire型的变量综合出来一般是一根导线; 2、 reg变量在always

完整的pdf格式文档51黑下载地址(共11页):

Verilog HDL数字系统设计.pdf

(490.37 KB, 下载次数: 52)

Verilog HDL数字系统设计.pdf

(490.37 KB, 下载次数: 52)

|