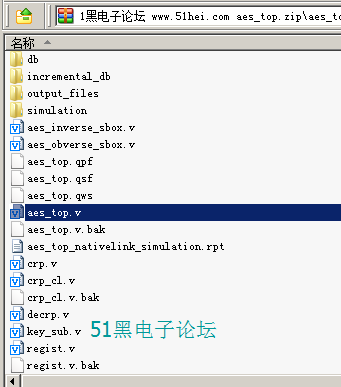

Quartus II可执行的Verilog代码 实现DEs AES加密和解密

全部资料51hei下载地址:

aes_top.zip

(7.4 MB, 下载次数: 87)

aes_top.zip

(7.4 MB, 下载次数: 87)

部分代码:

- //`timescale 1 ns/ 1 ps

- module aes_top

- (

- input clock,

- output reg over

- //input rst,

- //input flag,

- //input [32:1] indata,

- //output [32:1] outdata

- );

- reg rst;

- reg flag;

- //reg [32:1] indata;

- wire [32:1] outdata;

- wire overkey;

- wire overdecrp;

- wire overcrp;

- wire enkey,encrp,endecrp;

- wire [128:1] crp_out;

- wire [128:1] crp_in;

- wire [128:1] keyin;

- wire [128:1] key_out;

- wire [4:1] rn_key;

- reg [4:1] state=4'h0;

- integer i=0;

- integer j=0;

- parameter s0=4'h0,s1=4'h1,s2=4'h2,s3=4'h3,s4=4'h4,s5=4'h5,s6=4'h6;

- //assign over=clock;

- always @(posedge clock)

- begin

- case(state)

- s0:

- begin

- rst=0;

- flag=1;

- state=s1;

- over=0;

- end

- s1:

- begin

- rst=1;

- state=s2;

- end

- s2:

- begin

- if(overcrp==1||overdecrp==1)

- begin

- if(i==100)

- begin

- over=1;

- i=0;

- state=s3;

- end

- else if(i<100)

- begin

- i=i+1;

- state=s0;

- end

- end

- else

- state=s2;

- end

- s3:

- begin

- over=1;

- state=s4;

- end

- s4:

- begin

- over=1;

- if(j==10)

- begin

- j=0;

- state=s0;

- end

- else if(j<10)

- begin

- j=j+1;

- state=s3;

- end

- end

- endcase

- end

- regist regist

- (

- //.indata(indata),

- .clock(clock),

- .rst(rst),

- .overkey(overkey),

- .flag(flag),

- .overcrpc(overcrp),

- .overcrpm(overdecrp),

- .outcrp(crp_out),

- .outdata(outdata),

- .data(crp_in),

- .key(keyin),

- .enkey(enkey),

- .encrpc(encrp),

- .encrpm(endecrp)

- );

- key_sub key_sub

- (

- .keyin(keyin),

- .enkey(enkey),

- .rn(rn_key),

- .clock(clock),

- .overkey(overkey),

- .keyout(key_out)

- );

- crp_cl crp_cl

- (

- .clock(clock),

- .encrp(encrp),

- .endecrp(endecrp),

- .datain(crp_in),

- .keyin(key_out),

- .rn_key(rn_key),

- .overcrp(overcrp),

- .overdecrp(overdecrp),

- .crp_out(crp_out)

- );

- endmodule

|