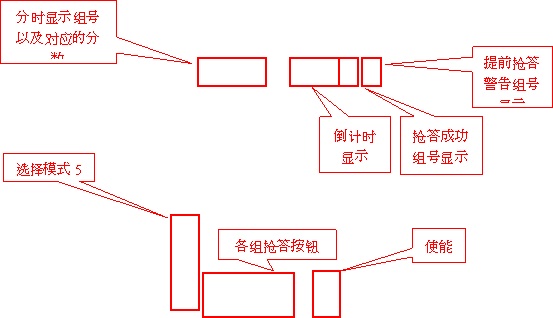

- ЩшМЦвЛИіЪ§зжЪНОКШќЧРД№Цї,ПЩвдХаЖЯЕквЛТжЧРД№еп,ВЂОпБИМЦЗжЙІФмЁЃ

- ЧРД№ЦїПЩвдШнФЩ4зщВЮШќепЭЌЪБЧРД№,УПзщЩшжУ1ИіАДХЅЙЉЧРД№епЪЙгУЁЃЩшжУЧРД№ЦїЪЙФмаХКХ,ЕБДЫаХКХгааЇЪБ,ШєВЮШќепАДЯТЧРД№ПЊЙи,дђЧРД№ЦїФмХаЖЯГіЕквЛЧРД№епВЂжИЪОИУзщЧРД№ГЩЙІ,ЦфЫћзщВЮШќепЕФЧРД№епЕФЧРД№ПЊЙиВЛЦ№зїгУЁЃШєЬсЧАЧРД№,дђЖдЯргІЕФВЮШќепЗЂГіБЈОЏЁЃ

- ЯЕЭГОпгаЧхСуЙІФмЁЃЕБЧхСуИДЮЛаХКХгааЇЪБ,ЧРД№ЦїЖдЧАвЛТжЧРД№ЕФЕквЛЧРД№епХаЖЯНсЙћНјааЧхСу,ЛжИДЮЊГѕЪМзДЬЌЁЃ

- Ъ§зжЪНОКШќЧРД№ЦїЛЙОпгаМЦЗжЙІФмЁЃШчЙћЧРД№ГЩЙІЕФВЮШќепТњзуЕУЗжЬѕМў,дђдіМгЯргІЕФЗжЪ§,Д№ДэВЛПлЗжЁЃ

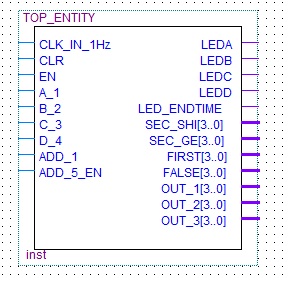

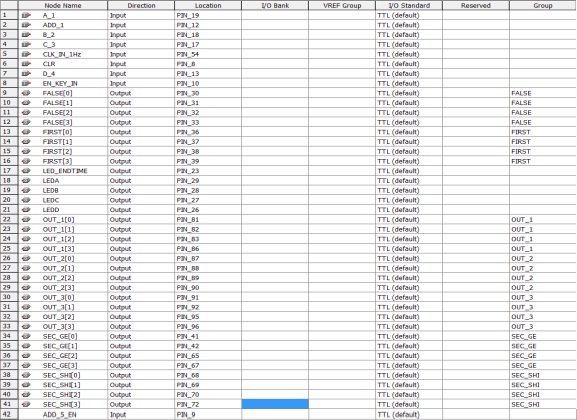

ЃЈЖўЃЉЯЕЭГЩшМЦЗНАИИљОнЯЕЭГЩшМЦвЊЧѓПЩжЊ,ЯЕЭГгЩ4ИіжївЊЕФЕчТЗФЃПщзщГЩ,ЗжБ№ЪЧЕквЛХаЖЯЕчТЗЁЂМЦЗжЕчТЗЁЂ20sЕЙМЦЪБЕчТЗКЭЯдЪОЕчТЗЁЃ   Цфжа,ЕквЛХаЖЯЕчТЗжївЊЭъГЩзюПьЧРД№епЕФХаЖЯЙІФм;МЦЗжЕчТЗДцДЂУПзщОКШќепЕФЗжЪ§;ЯдЪОЕчТЗдђЯдЪОЧРД№ЦїЕФзДЬЌКЭИїзщЕФЗжЪ§ЁЃвђДЫ,Ъ§зжЪНОКШќЧРД№ЦїЕФЪфШыаХКХАќРЈИДЮЛаХКХCLRЁЂЧРД№ЦїЪЙФмаХКХEN_KEY_INЁЂ4зщВЮШќепЕФЧРД№АДХЅA_1/B_2/C_3/D_4вдМАМгЗжаХКХADD_1ЃЌМг5ЗжЪЙФмаХКХADD_5_EN;ЪфГіаХКХАќРЈ4зщВЮШќепЧРД№зДЬЌЕФЯдЪОLEDx(xБэЪОВЮШќепБрКХ)МАЦфЖдгІЕФЕУЗжSCOREXЁЂЧРД№ЦїЧРД№ГЩЙІЕФзщБ№ЯдЪОЃЌзюЯШЧРД№зщЯдЪОFIRST[3..0]ЃЌЬсЧАЧРД№зщЯдЪОFALSE[3..0],ТжСїЪфГіИїзщКХвдМАЗжЪ§OUT_1,OUT_2,OUT_3ЕШЁЃЯЕЭГПђЭМШчЭМЫљЪОЃК

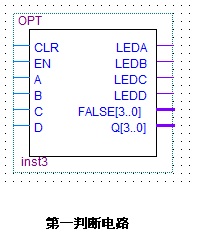

1. ЧРД№ЦїЕФЙЄзїСїГЬШчЯТЃКШчЙћВЮШќепдкЧРД№ЦїЪЙФмаХКХENгааЇЧААДЯТЧРД№АДХЅ,БЈОЏаХКХFALSE[3..0]ЕФЖдгІЮЛЪфГіИпЕчЦН,вдЪООЏИц;ЕБENаХКХгааЇЪБ,ЧРД№ЦїПЊЪМЙЄзї,НЋБЈОЏаХКХFALSEЧхСу,AЁЂBЁЂCЁЂD,4ИіЧРД№епЫЯШАДЯТЧРД№АДХЅ,дђЧРД№ГЩЙІ,ЖдгІЕФЯдЪОЕЦLEDxССЦ№,ВЂЭЈЙ§ЯдЪОЕчТЗФЃПщЯдЪОЦфВЮШќБрFIRST[3..0];ЧРД№ГЩЙІЕФбЁЪжНјШыД№ЬтНзЖЮ,Шче§ШЗЛиД№ЮЪЬт,дђМгЗжаХКХADDгааЇ,МЦЗжФЃПщИјЯргІЕФВЮШќзщМгЗж,УПИіВЮШќзщЕУЗжЕФИіЮЛЁЂЪЎЮЛЁЂАйЮЛЗжБ№ЭЈЙ§аХКХOUT_BCD1[3..0]ЁЂOUT_BCD2[3..0]ЁЂOUT_BCD3[3..0]ЁЂЯдЪОЁЃ ШчЙћИДЮЛаХКХCLRгааЇ,ЪЙЕУЧРД№ЦїдкЯТвЛТжЧРД№ЧА,ЦфЧРД№ГЩЙІЕФзщБ№ХаЖЯЛжИДЮЊЪМзДЬЌ,вдБужиаТПЊЪМаТвЛТжЧРД№ЁЃИДЮЛаХКХВЛИФБфОКШќепЕФЯжгаЕУЗжЁЃ 2.СїГЬЭМЃКЃЈШ§ЃЉжївЊФЃПщЩшМЦ1.0 ЕквЛХаЖЯЕчТЗЕквЛХаЖЯЕчТЗФЃПщОпгаЕквЛЧРД№аХКХЕФМјБ№КЭЫјДцЙІФм,ЦфЕчТЗПђЭМШчЭМЫљЪОЁЃ Цфжа,CLRЮЊИДЮЛаХКХ,ЕБИУаХКХИпЕчЦНгааЇЪБ,ЕчТЗЮоТлДІгкКЮжжзДЬЌЖМЛжИДЮЊГѕЪМзДЬЌМДЫљгаЕФЪфГіаХКХЖМЮЊ0;ENЮЊЧРД№ЪЙФмаХКХ,ИУаХКХИпЕчЦНгааЇ;AЁЂBЁЂCЁЂDЮЊЧРД№АДХЅ,ИпЕчЦНгааЇЁЃ  ЕБЪЙФмаХКХENЮЊЕЭЕчЦНЪБ,ШчЙћгаВЮШќепАДЯТЧРД№АДХЅ,дђЬсЧАЧРД№БЈОЏаХКХFALSE[3.0]ЕФЖдгІЮЛЪфГіИпЕчЦН,вдЪООЏИц;ЕБЪЙФмаХКХENЮЊИпЕчЦНЪБ,ЪзЯШНЋЬсЧАЧРД№БЈОЏаХКХFALSE [3.0]ИДЮЛЧхСу,ШЛКѓИљОнбЁЪжАДЯТЧРД№АДХЅAЁЂBЁЂCЁЂDЕФЯШКѓЫГЬќбЁдёзюЯШЧРД№ЕФаХКХ,ЦфЖдгІЕФЧРД№зДЬЌЯдЪОаХКХLEDA~LEDDЪфГіИпЕчЦН,ЧРД№ГЩЙІзщБ№БрКХгЩаХКХQ[3..0]ЪфГі,ВЂЫјДцЧРД№ЦїДЫЪБЕФ зДЬЌ,жБЕНЧхСуаХКХгааЇЮЊжЙЁЃдкУПвЛТжаТЕФЧРД№жЎЧА,ЖМвЊЪЙгУИДЮЛЧхСуаХКХCLR,ЧхГ§ЩЯвЛТжЧРД№ЖдХаЖЯЕчТЗСєЯТЕФЪЙгУКлМЃ,ЪЙЕчТЗЛжИДГѕЪМзДЬЌЁЃ

1.1 ЕквЛХаЖЯЕчТЗВЈаЮЗТецЭМ

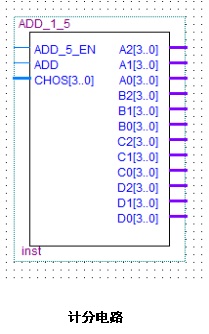

2.0 МЦЗжЕчТЗ  МЦЗжЕчТЗдкВЮШќепЧРД№ГЩЙІКѓ,ИљОнЦфБШШќЧщПіНјааБШНЯЗжЪ§ЕФЕїећ,ЦфЕчТЗПђЭМШчгвЭМЫљЪОЁЃИУФЃПщЪфШыаХКХЮЊМгЗжаХКХADD_1КЭзщБ№бЁдёаХКХCHOS[3.0]ЁЃ ЦфжаМгЗжаХКХADD_1ИпЕчЦНгааЇ,гааЇЪБЖдзщБ№бЁдёаХКХCHOS[3..0]бЁдёЕФВЮЪ§зщНјааМгЗж;зщБ№бЁдёЪфШыаХКХCHOS[3..0]МДЕквЛХаЖЯЕчТЗФЃПщЕФЪфГіаХКХQ [3.0]ЁЃЪфГіаХКХЗжБ№ЖдгІ4зщОКШќепЕФЕУЗж,вдАйЗжжЦБэЪОЁЃУПзщЗжЪ§дкБШШќПЊЪМЪБдЄЩшЮЊ100Зж,УПД№Жд1Ьт(МДМгЗжбЁдёаХКХЖдЯргІВЮШќзщгааЇ)Мг1Зж,Д№ДэВЛПлЗжЁЃЕУЗжЕФИїЮЛЁЂЪЎЮЛЁЂАйЮЛБэЪОЮЊПэЮЊ4ЕФТпМЪИСП,ЪЙжЎЗНБугыЯдЪОЕчТЗМЖСЊ,ДгЖјЪфГіБШШќЕУЗжЁЃ ЕБМг5ЗжЪЙФмаХКХADD_5_ENЮЊИпЕчЦНЪБADDУПАДвЛДЮМг5Зж

2.1 МЦЗжЕчТЗВЈаЮЗТецЭМ

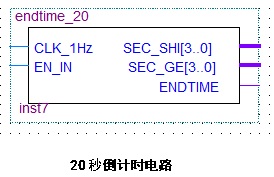

3.0 ЕЙМЦЪБЕчТЗЕЙМЦЪБЕчТЗгУРДМЧТМе§ГЃЧРД№ПЊЪМКѓЕФЪБМфЃЌЖЈЪБЮЊ20УыЃЌдк20УыФкЧРД№гааЇЃЌЗёдђИУЬтзїЗЯЁЃЦфЕчТЗЭМШчгвЭМЃК

ЦфжаЃЌCLK_1HzЪЧЪБжгаХКХЃЌЦЕТЪЮЊ1HzЃЌгУРДМЦЪБЃЌМфИєЮЊ1УыЃЛEN_INЪЧЪЙФмаХКХЃЌИпЕчЦНгааЇПЊЪМЕЙМЦЪБЃЌENDTIMEЪфГіаХКХЃЌгУРДЬсЪОЪБМфЕНЃЌСЌНгLEDЕЦЃЌЕБЪБМфЮЊ0ЪБЪфГіИпЕчЦНЃЌledЕЦЕуССЁЃSEC_SHI[3..0]ЁЂSEC_GE[3..0]ЗжБ№ЪЧЕЙМЦЪБЕФЪЎЮЛКЭИїЮЛЃЌСЌНгДјвыТыЦїЕФЪ§ТыЙм,гУРДЯдЪОЕЙМЦЪБЕФЪБМфЁЃ

3.1 ЕЙМЦЪБЕчТЗВЈаЮЗТецЭМ

4.0 ЯдЪОЕчТЗ  ЯдЪОЕчТЗгУРДТжСїЯдЪОИїзщЕФЕУЗжЧщПіЁЃгЩгкЪЕбщЯфЪ§ТыЙмгаЯоЃЌЫљвдВЩгУСЫЪ§ТыЙмЗжЪБИДгУЕФЗНЗЈРДЯдЪОИїзщЕФЕУЗжЧщПіЁЃЦфЕчТЗПђЭМШчгвЭМЃК

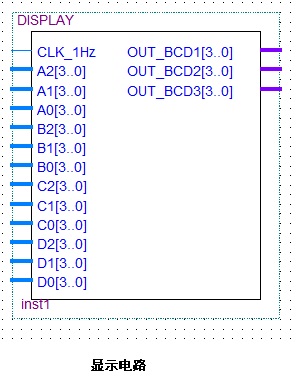

ЯдЪОЕчТЗжаA2[3..0]ЁЂA1[3..0]ЁЂA0[3..0]ЃЛB2[3..0]ЁЂB1[3..0]ЁЂB0[3..0]ЃЛC2[3..0]ЁЂC1[3..0]ЁЂC0[3..0]ЁЃЪЧИїзщЗжЪ§ЕФАйЮЛЁЂЪЎЮЛЁЂвдМАИїЮЛЁЃOUT_BCD1[3..0]ЁЂOUT_BCD2[3..0]ЁЂOUT_BCD3[3..0]гУРДЪфГіжСДјгавыТыЦїЕФЪ§ТыЙмЃЌгУгкЗжЪБЯдЪОИїзщКХвдМАЖдгІЕФЗжЪ§ЁЃCLK_1HzЪЧЪфШыЕФЪБжгаХКХЃЌЦЕТЪЮЊ1HzЃЌгУРДМфИє1УыТжСїЯдЪОЁЃ ЦфЗжЪБЯдЪОСїГЬШчЯТЃК 4.1 ЯдЪОЕчТЗВЈаЮЗТец

4.2ЯдЪОЕчТЗЗжЪБЯдЪОИїзщЗжЪ§СїГЬЭМ:

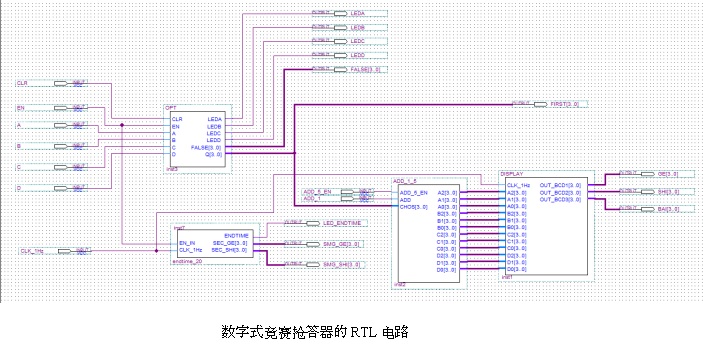

ЃЈЫФЃЉЯЕЭГећЬхдРэЭМ ЩЯЪіVHDLдДГЬађЙЙГЩСЫвЛИіОпгаЧРД№ЁЂМЦЗжЁЂЕЙМЦЪБОЏБЈЙІФмЕФЪ§зжЯЕЭГ,ЭЈЙ§ЗТецЩњГЩЕФRTLЕчТЗШчЭМЫљЪО:

ЭМжа,ЪфГіFALSE[3..0]ЁЂGE[3..0] ЁЂSHI[3..0]ЁЂBAI[3..0] ЁЂFIRST[3..0]ЁЂSMG_GE[3..0] ЁЂSMG_SHI[3..0]ЛЙашвЊЭЈЙ§LEDЙВвѕМЋвыТыЦївыТыЯдЪОЮЊЪЎНјжЦЪ§,выТыЯдЪОЕчТЗВПЗждкДЫТдЙ§ЁЃжЕЕУзЂвтЕФЪЧЕквЛЧРД№ХаЖЯЕчТЗФЃПщЕФЪфГіаХКХQ[3..0],ЫќМШЪЧећИіЪ§зжЪНЧРД№ЦїЪфГіЕФвЛВПЗж,ЯдЪОЧРД№ГЩЙІЕФбЁЪжБрКХ,гжзїЮЊМЦЗжФЃПщЕФЪфШыаХКХ,вдЫќЮЊвРОнЖдЯргІЕФбЁЪжНјааМгЗжВйзїЁЃ

ЃЈЮхЃЉЯЕЭГВЈаЮЗТецЕквЛЧРД№ХаЖЯФЃПщЕФЗТецВЈаЮШчЯТЭМЫљЪОЁЃДгЭМжаПЩвдПДГі,ЕБЧхСуИДЮЛаХКХCLRИпЕчЦНгааЇЪБ,ЕчТЗзДЬЌСЂПЬБЛЛжИДЮЊШЋ0ЕФГѕЪМзДЬЌЁЃдкЧРД№ЪЙФмаХКХЮоаЇЪБЧРД№,ЪфГіОЏИцаХКХ,ЬсЧАЧРД№епЖдгІЕФзщКХЛсгУЪ§ТыЙмЪфГі,вдЪООЏИцЁЃ ЕБЧРД№ЪЙФмаХКХИпЕчЦНгааЇЪБ,зюЯШЧРД№ЕФбЁЪжЖдгІЕФЯдЪОЕЦLEDxССЦ№,Q[3..0]ЪфГіЧРД№ГЩЙІЕФбЁЪжБрКХЁЃЗТецНсЙћгыЯЕЭГЩшМЦвЊЧѓЕФЙІФмЯрЮЧКЯЁЃ ЪфШыаХКХCHOS[3.0]вдЪЎНјжЦЕФаЮЪНБэЪО,1,2,3,4,8ЗжБ№ДњБэбЁдёABЁЂCЁЂD4зщбЁЪждкМгЗжаХКХADD_1ЕФЩЯЩ§биЖдбЁжаЕФВЮШќепНјааМгЗж,ДгИпжСЕЭвРДЮЮЊАйЮЛЁЂЪЎЮЛЁЂИіЮЛЁЃ 1

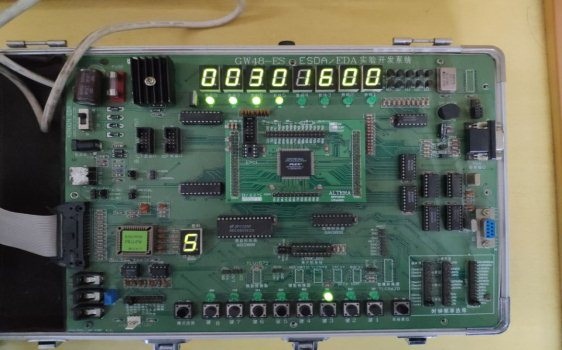

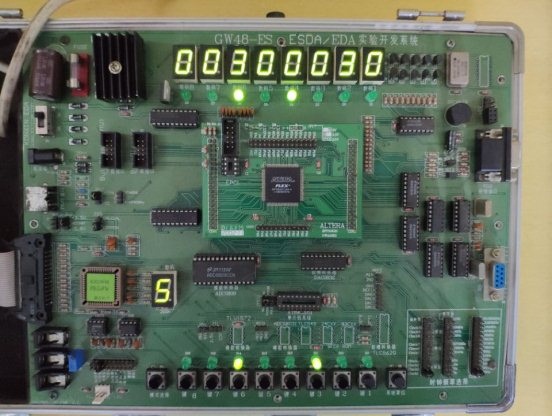

ЃЈЦпЃЉФЃЪНбЁдёИљОнЪЕМЪЧщПіЃЌгІбЁдёЃКФЃЪН5. бЁдёРэгЩЃКФЃЪН5ДјгавыТыЦїаОЦЌЃЌПЩвдМѕЩйвыТыЕчТЗЁЃДјгаЖдгІЕФledЕЦвдМАЪ§ТыЙмЃЌБугкЯдЪОЖдгІЕФзщКХЁЃЭЌЪБФЃЪН5га8ИіМќПиИпЕЭЕчЦНЗЂЩњЦїЃЌПЩвдТњзуЧРД№ЦїЕчТЗЕФашЧѓЁЃ  ЃЈАЫЃЉв§НХАѓЖЈ ЃЈАЫЃЉв§НХАѓЖЈ

ЃЈОХЃЉЪдбщЯфВтЪдЭМ ЁО1ЁППЊЪМЧРД№ЁЃ   ЁО2ЁП3КХзщЧРД№ГЩЙІЁЃ  ЁО3ЁПНјааМгЗжЃЌМг5ЗжЁЃ ЁО4ЁПЧхСуЃЌзМБИЯТвЛДЮЧРД№ЁЃ

ЃЈЪЎЃЉзмНсЃКгкИіШЫЃЌЭЈЙ§етДЮЩшМЦЃЌЮвНјвЛВНМгЩюСЫЖдЕчзгЩшМЦЕФСЫНтЁЃВЂНјвЛВНЪьСЗСЫЖдQuartusIIШэМўЕФВйзїЃЌЛљБОеЦЮеСЫVHDLетУХгВМўБрГЬгябдЁЃEDAвВВЛЯёбЇЯАРэТлАуФЧУДПеЖДЃЌгаСЫИќМгЬљЧаЕФСЫНтМАдЫгУЁЃзіЩшМЦЪБЃЌЯШВщдФЯрЙижЊЪЖЃЌАбдРэГдЭИЃЌШЗЖЈвЛИіДѓЕФЩшМЦЗНЯђЃЌдкАДееетИіЗНЯђЗжФЃПщЕФАбвЊЪЕЯжЕФЙІФмгУСїГЬЭМЕФаЮЪНеЙЪОЁЃзюКѓВЮееУПИіФЃПщАбЪфШыКЭЪфГів§НХЩшЖЈЃЌдЫгУЮвУЧЫљбЇЕФVHDLгябдНјааБрГЬЁЃзмжЎЃЌЭЈЙ§етДЮЕФЩшМЦЃЌНјвЛВНСЫНтСЫEDAММЪѕЃЌЪеЛёКмДѓЃЌЖдШэМўБрГЬЁЂХХДэЕїЪдЁЂЯрЙивЧЦїЩшБИЕФЪЙгУММФмЕШЗНУцЕУЕННЯШЋУцЕФЖЭСЖКЭЬсИп

- ГЬађЃК

- --ЖЅВуФЃПщЕФVHDL

- LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- ENTITY TOP_ENTITY IS

- PORT

- (

- CLK_IN_1Hz:IN STD_LOGIC;

- CLR:IN STD_LOGIC; --ЧхСуаХКХ

- EN_KEY_IN:IN STD_LOGIC; --ЧРД№ПЊЪМаХКХ ИпЕчЦНгааЇ

- A_1,B_2,C_3,D_4:IN STD_LOGIC;

- ADD_1:IN STD_LOGIC; --МгЗжаХКХ

- LEDA,LEDB,LEDC,LEDD,LED_ENDTIME:OUT STD_LOGIC;

- SEC_SHI:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

- SEC_GE:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

- FIRST:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

- FALSE:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

- OUT_1:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --ЯдЪОИіЮЛ ЪЎЮЛ АйЮЛ

- OUT_2:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

- OUT_3:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)

- );

- END ENTITY TOP_ENTITY;

- ARCHITECTURE RTL OF TOP_ENTITY IS

- COMPONENT OPT IS

- PORT (

- CLR:IN STD_LOGIC; --ИДЮЛаХКХ

- EN :IN STD_LOGIC; --ЧРД№ЪЙФмаХКХ

- A,B,C,D:IN STD_LOGIC; --ЧРД№АДХЅ

- LEDA:OUT STD_LOGIC;

- LEDB:OUT STD_LOGIC;

- LEDC:OUT STD_LOGIC;

- LEDD:OUT STD_LOGIC;

- FALSE:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --ЬсЧАЧРД№ОЏБЈ

- Q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0) --ЧРД№ГЩЙІзщЯдЪО

- );

- END COMPONENT OPT;

- COMPONENT COUNTER IS

- PORT

- (

- ADD_1:IN STD_LOGIC; --МгЗжаХКХ

- CHOS:IN STD_LOGIC_VECTOR(3 DOWNTO 0); --ВЮШќзщбЁдёаХКХ

- A2,A1,A0:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --ИїзщМЦЗжаХКХ

- B2,B1,B0:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

- C2,C1,C0:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

- D2,D1,D0:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)

- );

- END COMPONENT COUNTER;

- COMPONENT OUTPUT IS --ЬсЧАЧРД№ОЏИц

- PORT

- (

- DIN:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

- DOUT:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)

- );

- END COMPONENT OUTPUT;

- COMPONENT endtime_20 IS

- PORT

- (

- CLK_1Hz :IN STD_LOGIC; --ЪБжгаХКХ

- EN_in :IN STD_LOGIC; --ЪЙФм МЦЪБПЊЪМ

- SEC_SHI:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --УыИїЮЛ BCD 4ЮЛ2НјжЦЪфГі

- SEC_GE:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --УыАйЮЛ BCD 4ЮЛ2НјжЦЪфГі

- ENDTIME:OUT STD_LOGIC --ЪБМфЕНОЏБЈ НгЗфУљЦї

- );

- END COMPONENT endtime_20;

- COMPONENT DISPLAY IS

- PORT

- (

- CLK_1Hz:IN STD_LOGIC;

- A2,A1,A0:IN STD_LOGIC_VECTOR(3 DOWNTO 0); --ИїзщМЦЗжаХКХ

- B2,B1,B0:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

- C2,C1,C0:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

- D2,D1,D0:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

- OUT_BCD1:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --ЪфГіИіЪЎАйЮЛ

- OUT_BCD2:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

- OUT_BCD3:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)

- );

- END COMPONENT DISPLAY;

- SIGNAL Q:STD_LOGIC_VECTOR(3 DOWNTO 0);

- SIGNAL AA2,AA1,AA0:STD_LOGIC_VECTOR(3 DOWNTO 0);

- SIGNAL BB2,BB1,BB0:STD_LOGIC_VECTOR(3 DOWNTO 0);

- SIGNAL CC2,CC1,CC0:STD_LOGIC_VECTOR(3 DOWNTO 0);

- SIGNAL DD2,DD1,DD0:STD_LOGIC_VECTOR(3 DOWNTO 0);

- BEGIN

- U1:OPT PORT MAP(CLR,EN_KEY_IN,A_1,B_2,C_3,D_4,LEDA,LEDB,LEDC,LEDD,FALSE,Q);

- U2:COUNTER PORT MAP(ADD_1,Q,AA2,AA1,AA0,BB2,BB1,BB0,CC2,CC1,CC0,DD2,DD1,DD0);

- U3:OUTPUT PORT MAP(Q,FIRST);

- U4:DISPLAY PORT MAP(CLK_IN_1Hz,AA2,AA1,AA0,BB2,BB1,BB0,CC2,CC1,CC0,DD2,DD1,DD0,OUT_1,OUT_2,OUT_3);

- U5:endtime_20 PORT MAP(CLK_IN_1Hz,EN_KEY_IN,SEC_SHI,SEC_GE,LED_ENDTIME);

- END ARCHITECTURE RTL;

- --ЕквЛЧРД№ХаЖЯ ЕчТЗ ЕФVHDLГЬађ

- LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- ENTITY OPT IS

- PORT (

- CLR:IN STD_LOGIC; --ИДЮЛаХКХ

- EN :IN STD_LOGIC; --ЧРД№ЪЙФмаХКХ

- A,B,C,D:IN STD_LOGIC; --ЧРД№АДХЅ

- LEDA:OUT STD_LOGIC:='0'; --ЧРД№ГЩЙІ ЖдгІзщЕФledЕЦЕуСС

- LEDB:OUT STD_LOGIC:='0';

- LEDC:OUT STD_LOGIC:='0';

- LEDD:OUT STD_LOGIC:='0';

- FALSE:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --ЬсЧАЧРД№ОЏБЈ

- Q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0) --ЧРД№ГЩЙІзщЯдЪО

- );

- END ENTITY OPT;

- ARCHITECTURE RTL OF OPT IS

- SIGNAL TMP:STD_LOGIC_VECTOR(3 DOWNTO 0);

- SIGNAL TAG:STD_LOGIC;

- BEGIN

- TMP<=A&B&C&D;

- PROCESS(CLR,EN,A,B,C,D,TMP,TAG)

- BEGIN --ЩшжУЫјДцБъжОЮЛ

- IF CLR='1' THEN

- Q<="0000";

- LEDA<='0';

- LEDB<='0';

- LEDC<='0';

- LEDD<='0';

- FALSE<="0000";

- TAG<='0';

- ELSIF EN='0' THEN

- IF TAG='0' THEN

- IF A='1' THEN

- FALSE(0)<='1';

- END IF;

- IF B='1' THEN

- FALSE(1)<='1';

- END IF;

- IF C='1' THEN

- FALSE(2)<='1';

- END IF;

- IF D='1' THEN

- FALSE(3)<='1';

- END IF;

- END IF;

- ELSE

- FALSE<="0000";

- IF TAG='0' THEN

- IF TMP="1000" THEN

- LEDA<='1';

- LEDB<='0';

- LEDC<='0';

- LEDD<='0';

- Q<="0001";

- TAG<='1';

- ELSIF TMP="0100"THEN

- LEDA<='0';

- LEDB<='1';

- LEDC<='0';

- LEDD<='0';

- Q<="0010";

- TAG<='1';

- ELSIF TMP="0010"THEN

- LEDA<='0';

- LEDB<='0';

- LEDC<='1';

- LEDD<='0';

- Q<="0011";

- TAG<='1';

- ELSIF TMP="0001"THEN

- LEDA<='0';

- LEDB<='0';

- LEDC<='0';

- LEDD<='1';

- Q<="0100";

- TAG<='1';

- ELSE

- LEDA<='Z';

- LEDB<='Z';

- LEDC<='Z';

- LEDD<='Z';

- Q<="ZZZZ";

- END IF;

- END IF;

- END IF;

- END PROCESS;

- END RTL;

-

- --МЦЗжЕчТЗЕФVHDLГЬађ ADD_1 ADD_5

- LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- USE IEEE.STD_LOGIC_ARITH.ALL;

- ENTITY ADD_1_5 IS

- PORT

- (

- ADD_5_EN,ADD:IN STD_LOGIC; --МгЗжаХКХ

- CHOS:IN STD_LOGIC_VECTOR(3 DOWNTO 0); --ВЮШќзщбЁдёаХКХ

- A2,A1,A0:OUT STD_LOGIC_VECTOR(3 DOWNTO 0):="0000"; --ИїзщМЦЗжаХКХ

- B2,B1,B0:OUT STD_LOGIC_VECTOR(3 DOWNTO 0):="0000";

- C2,C1,C0:OUT STD_LOGIC_VECTOR(3 DOWNTO 0):="0000";

- D2,D1,D0:OUT STD_LOGIC_VECTOR(3 DOWNTO 0):="0000"

- );

- END ENTITY ADD_1_5;

- ARCHITECTURE RTL OF ADD_1_5 IS

- BEGIN

- PROCESS(ADD,ADD_5_EN,CHOS)

- VARIABLE POINTS_A2,POINTS_A1,POINTS_A0:STD_LOGIC_VECTOR(3 DOWNTO 0):="0000";

- VARIABLE POINTS_B2,POINTS_B1,POINTS_B0:STD_LOGIC_VECTOR(3 DOWNTO 0):="0000";

- VARIABLE POINTS_C2,POINTS_C1,POINTS_C0:STD_LOGIC_VECTOR(3 DOWNTO 0):="0000";

- VARIABLE POINTS_D2,POINTS_D1,POINTS_D0:STD_LOGIC_VECTOR(3 DOWNTO 0):="0000";

- BEGIN

- IF ADD_5_EN='1' THEN

- IF ADD='1' AND ADD'EVENT THEN

- CASE CHOS IS

- WHEN "0001" => FOR I IN 0 TO 4 LOOP

- IF POINTS_A0="1001" THEN

- POINTS_A0:="0000";

- IF POINTS_A1="1001" THEN

- POINTS_A1:="0000";

- IF POINTS_A2="1001" THEN --ЪЎЮЛЗж9

- POINTS_A2:="0000"; --ЪЎЮЛЧхСу

- ELSE

- POINTS_A2:=POINTS_A2+'1';

- END IF;

- ELSE

- POINTS_A1:=POINTS_A1+'1';

- END IF;

- ELSE

- POINTS_A0:=POINTS_A0+'1';

- END IF;

- END LOOP;

- WHEN "0010" => FOR I IN 0 TO 4 LOOP

- IF POINTS_B0="1001" THEN

- POINTS_B0:="0000";

- IF POINTS_B1="1001" THEN

- POINTS_B1:="0000";

- IF POINTS_B2="1001" THEN --ЪЎЮЛЗж9

- POINTS_B2:="0000"; --ЪЎЮЛЧхСу

- ELSE

- POINTS_B2:=POINTS_B2+'1';

- END IF;

- ELSE

- POINTS_B1:=POINTS_B1+'1';

- END IF;

- ELSE

- POINTS_B0:=POINTS_B0+'1';

- END IF;

- END LOOP;

- WHEN "0011" => FOR I IN 0 TO 4 LOOP

- IF POINTS_C0="1001" THEN

- POINTS_C0:="0000";

- IF POINTS_C1="1001" THEN

- POINTS_C1:="0000";

- IF POINTS_C2="1001" THEN --ЪЎЮЛЗж9

- POINTS_C2:="0000"; --ЪЎЮЛЧхСу

- ELSE

- POINTS_C2:=POINTS_C2+'1';

- END IF;

- ELSE

- POINTS_C1:=POINTS_C1+'1';

- END IF;

- ELSE

- POINTS_C0:=POINTS_C0+'1';

- END IF;

- END LOOP;

- WHEN "0100" => FOR I IN 0 TO 4 LOOP

- IF POINTS_D0="1001" THEN

- POINTS_D0:="0000";

- IF POINTS_D1="1001" THEN

- POINTS_D1:="0000";

- IF POINTS_D2="1001" THEN --ЪЎЮЛЗж9

- POINTS_D2:="0000"; --ЪЎЮЛЧхСу

- ELSE

- POINTS_D2:=POINTS_D2+'1';

- END IF;

- ELSE

- POINTS_D1:=POINTS_D1+'1';

- END IF;

- ELSE

- POINTS_D0:=POINTS_D0+'1';

- END IF;

- END LOOP;

- WHEN OTHERS => NULL;

- END CASE;

- END IF;

- ELSE

- IF ADD='1' AND ADD'EVENT THEN

- CASE CHOS IS

- WHEN "0001" => IF POINTS_A0="1001" THEN

- POINTS_A0:="0000";

- IF POINTS_A1="1001" THEN

- POINTS_A1:="0000";

- IF POINTS_A2="1001" THEN --ЪЎЮЛЗж9

- POINTS_A2:="0000"; --ЪЎЮЛЧхСу

- ELSE

- POINTS_A2:=POINTS_A2+'1';

- END IF;

- ELSE

- POINTS_A1:=POINTS_A1+'1';

- END IF;

- ELSE

- POINTS_A0:=POINTS_A0+'1';

- END IF;

- WHEN "0010" => IF POINTS_B0="1001" THEN

- POINTS_B0:="0000";

- IF POINTS_B1="1001" THEN

- POINTS_B1:="0000";

- IF POINTS_B2="1001" THEN --ЪЎЮЛЗж9

- POINTS_B2:="0000"; --ЪЎЮЛЧхСу

- ELSE

- POINTS_B2:=POINTS_B2+'1';

- END IF;

- ELSE

- POINTS_B1:=POINTS_B1+'1';

- END IF;

- ELSE

- POINTS_B0:=POINTS_B0+'1';

- END IF;

- WHEN "0011" => IF POINTS_C0="1001" THEN

- POINTS_C0:="0000";

- IF POINTS_C1="1001" THEN

- POINTS_C1:="0000";

- IF POINTS_C2="1001" THEN --ЪЎЮЛЗж9

- POINTS_C2:="0000"; --ЪЎЮЛЧхСу

- ELSE

- POINTS_C2:=POINTS_C2+'1';

- END IF;

- ELSE

- POINTS_C1:=POINTS_C1+'1';

- END IF;

- ELSE

- POINTS_C0:=POINTS_C0+'1';

- END IF;

- WHEN "0100" => IF POINTS_D0="1001" THEN

- POINTS_D0:="0000";

- IF POINTS_D1="1001" THEN

- POINTS_D1:="0000";

- IF POINTS_D2="1001" THEN --ЪЎЮЛЗж9

- POINTS_D2:="0000"; --ЪЎЮЛЧхСу

- ELSE

- POINTS_D2:=POINTS_D2+'1';

- END IF;

- ELSE

- POINTS_D1:=POINTS_D1+'1';

- END IF;

- ELSE

- POINTS_D0:=POINTS_D0+'1';

- END IF;

- WHEN OTHERS => NULL;

- END CASE;

- END IF;

- END IF;

- A2<=POINTS_A2;A1<=POINTS_A1;A0<=POINTS_A0;

- B2<=POINTS_B2;B1<=POINTS_B1;B0<=POINTS_B0;

- C2<=POINTS_C2;C1<=POINTS_C1;C0<=POINTS_C0;

- D2<=POINTS_D2;D1<=POINTS_D1;D0<=POINTS_D0;

- END PROCESS;

- END RTL;

- --ЯдЪОЬсЧАЧРД№зщЕчТЗЕФVHDLГЬађ

- LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- ENTITY OUTPUT IS

- PORT

- (

- DIN:IN STD_LOGIC_VECTOR(3 DOWNTO 0); --ЪфШыЬсЧАЧРД№ЕФзщКХ

- DOUT:OUT STD_LOGIC_VECTOR(3 DOWNTO 0) --ЪфГіЬсЧАЧРД№ЕФзщКХ

- );

- END ENTITY OUTPUT;

- ARCHITECTURE RTL OF OUTPUT IS

- BEGIN

- PROCESS(DIN)

- BEGIN

- CASE DIN IS

- WHEN"0001"=>DOUT<="0001";

- WHEN"0010"=>DOUT<="0010";

- WHEN"0011"=>DOUT<="0011";

- WHEN"0100"=>DOUT<="0100";

- WHEN OTHERS=>DOUT<="0000";

- END CASE;

- END PROCESS;

- END RTL;

- --ЖЏЬЌИїзщЗжЪ§ЯдЪО ТжСїЯдЪО

- LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- ENTITY DISPLAY IS

- PORT

- (

- CLK_1Hz:IN STD_LOGIC;

- A2,A1,A0:IN STD_LOGIC_VECTOR(3 DOWNTO 0); --ИїзщМЦЗжаХКХ

- B2,B1,B0:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

- C2,C1,C0:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

- D2,D1,D0:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

-

- OUT_BCD1:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --ЪфГіИіЪЎАйЮЛ

- OUT_BCD2:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

- OUT_BCD3:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)

- );

- END ENTITY DISPLAY;

- ARCHITECTURE BEHAVE OF DISPLAY IS

- SIGNAL FILG:STD_LOGIC_VECTOR(2 DOWNTO 0):="000";

- BEGIN

- PROCESS(CLK_1Hz,FILG)

- BEGIN

- IF CLK_1Hz'EVENT AND CLK_1Hz='1' THEN

- FILG<=FILG+'1';

- END IF;

-

- CASE FILG IS --ЖЏЬЌбЛЗЯдЪО

- WHEN "000" => OUT_BCD1<="0001"; --ЕквЛТжЯдЪОзщКХ

- WHEN "001" => OUT_BCD1<=A0; --ЕкЖўТжЯдЪОЗжЪ§

- OUT_BCD2<=A1;

- OUT_BCD3<=A2;

-

- WHEN "010" => OUT_BCD1<="0010";

- WHEN "011" => OUT_BCD1<=B0;

- OUT_BCD2<=B1;

- OUT_BCD3<=B2;

-

- WHEN "100" => OUT_BCD1<="0011";

- WHEN "101" => OUT_BCD1<=C0;

- OUT_BCD2<=C1;

- OUT_BCD3<=C2;

-

- WHEN "110" => OUT_BCD1<="0100";

- WHEN "111" => OUT_BCD1<=D0;

- OUT_BCD2<=D1;

- OUT_BCD3<=D2;

- END CASE;

- END PROCESS;

- END ARCHITECTURE BEHAVE;

-

- --20УыЕЙМЦЪБ ЯдЪО

- LIBRARY IEEE;

- USE IEEE.STD_LOGIC_1164.ALL;

- USE IEEE.STD_LOGIC_UNSIGNED.ALL;

- USE IEEE.STD_LOGIC_ARITH.ALL;

- ENTITY endtime_20 IS

- PORT

- (

- CLK_1Hz :IN STD_LOGIC; --ЪБжгаХКХ

- EN_IN :IN STD_LOGIC; --ЪЙФм МЦЪБПЊЪМ

- SEC_SHI:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --УыИїЮЛ BCD 4ЮЛ2НјжЦЪфГі

- SEC_GE:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --УыАйЮЛ BCD 4ЮЛ2НјжЦЪфГі

- ENDTIME:OUT STD_LOGIC --ЪБМфЕНОЏБЈ НгЗфУљЦї

- );

- END ENTITY endtime_20 ;

- ARCHITECTURE BEHAVE OF endtime_20 IS

- SIGNAL CONTER_20:STD_LOGIC_VECTOR(4 DOWNTO 0):="00000";

- BEGIN

- PROCESS(CLK_1Hz,EN_IN)

- BEGIN

- IF EN_IN='1' THEN

- IF CLK_1Hz='1' AND CLK_1Hz'EVENT THEN

- CASE CONTER_20 IS

- WHEN "00000" =>SEC_SHI<="0010"; --20

- SEC_GE<="0000";

- CONTER_20<=CONTER_20+'1';

-

- ENDTIME<='0';

- WHEN "00001" =>SEC_GE<="1001";--19

- SEC_SHI<="0001";

- CONTER_20<=CONTER_20+'1';

-

- WHEN "00010" =>SEC_GE<="1000";--18

- SEC_SHI<="0001";

- CONTER_20<=CONTER_20+'1';

-

- WHEN "00011" =>SEC_GE<="0111";--17

- SEC_SHI<="0001";

- CONTER_20<=CONTER_20+'1';

-

- WHEN "00100" =>SEC_GE<="0110";--16

- SEC_SHI<="0001";

- CONTER_20<=CONTER_20+'1';

-

- WHEN "00101" =>SEC_GE<="0101";--15

- SEC_SHI<="0001";

- CONTER_20<=CONTER_20+'1';

-

- WHEN "00110" =>SEC_GE<="0100";--14

- SEC_SHI<="0001";

- CONTER_20<=CONTER_20+'1';

- ЁЁЁЁЁЁЁЁ

- ЁЁЁЁЯогкБОЮФЦЊЗљ грЯТДњТыЧыДг51КкЯТдиИНМўЁЁЁЁ

ШЋВПзЪСЯ51heiЯТдиЕижЗЃК

END_DESITN_SECOND.rar

(3.36 MB, ЯТдиДЮЪ§: 54)

END_DESITN_SECOND.rar

(3.36 MB, ЯТдиДЮЪ§: 54)

|

ЙмРэдБQQ:125739409;ММЪѕНЛСїQQШК281945664

ЙмРэдБQQ:125739409;ММЪѕНЛСїQQШК281945664