在网上看到的一遍文章,觉的不错,分享给大家

单片的输入输出不叫GPIO,仅仅是个io,稍微复杂点的就是串口,至于后面那些增强的1t的带da的单片机,都不属于入门学习范围.那些东西都是为了低成本而存在,对学习没有任何作用.只要初学者入门了,所有片内外设都非常简单的搞定.本文是一片基础学习文章.入门者的精神食粮.

理解gpio不仅仅是会配置寄存器,因为好多人根本不知道寄存器如何配置.如果不信的话那回答我这个问题,stm32的io频率到底该配置成多少Mhz?

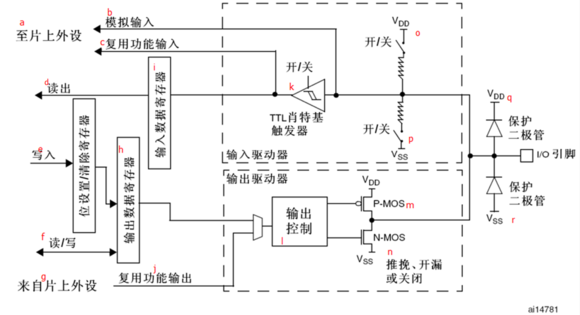

上面这张图是来自stm32的中文版手册.我对这些模块进行了简单的标注.下面我就从外到内进行分析信号的流向以及每一部分存在/屏蔽的意义.

先看上半部分,就是io的I,input,输入功能.信号从io引脚流入,首先被保护二极管q/r进行钳位.那就举一个例子,假定vdd是3.3v,那么二极管有0.7v的压降,那么io引脚的高电平就不能超过3.3+0.7v=4v只要超过4v那么就会有很大的电流从保护二极管流过,信号的内阻就会承担比较大的电压,使io引脚的电压最高钳位到4v.上面分析的是对于过高的电平.q二极管导通.r二极管关闭,所以不用分析.对于io出现负电压,这个时候q二极管是关闭的需要分析下面的r二极管.r二极管保持io引脚电平不低于vss-0.7v.至于为什么会出现这种情况,暂时不做分析,如果你看过示波器的振铃信号.就明白了.给大家留一个问题,如何消除振铃信号?

对于正常的数字信号,就进入了o/p电阻的控制范围.上下拉电阻的作用又是什么,什么时候需要上下拉? 上拉电阻就是在信号和vdd直接接引ig电阻,经验值在10k左右.对于一个5v的信号,能够最大提供0.5ma的电流.首先聊一个开漏输出,就是iic使用的信号.这种信号的两个状态是Z高阻态和0低电平,无法提供高电平的.加入一个上拉电阻,就能在z态的时候,信号线为高电平vdd, 0态的时候信号线为0.上拉电阻承担整个vdd电压.也就是说z态的时候上拉电阻无电流通过,功耗基本为0,而0态的时候上拉电阻功率为vdd*vdd/r,在低功耗设计的时候这一个电阻的功耗需要考虑.默认状态需要保持电阻在功耗0的状态.当然对于stm32这种片内控制的上下拉,直接关掉,让其浮空.就会降低功耗.但是有可能信号也失去了意义无法唤醒cpu.慎重严肃考虑.上拉电阻的意义就是给总线灌入一定电流,提高总线从0到1跳变的速度.有些信号驱动能力不足的时候,会提供信号的高电平驱动能力.包括电压和电流.相反,减缓了下降沿的速度,降低了低电平的驱动能力.在设计的时候多用欧姆定律计算.包括功耗.电阻究竟该用多大.

K元件,呵呵.这个是个很有意思的东西.其实这里的每一个元件都有意思,否则 2个电阻2个二极管就不需要写上面的两大段了.首先名称是ttl肖特基触发器,不就是个带门限的触发器嘛.首先ttl是指他的参考是ttl电平不是cmos电平,这里写详细了大家也会混乱.ttl电平我解释一下,TTL输出高电平>2.4V,输出低电平<0.4V。最小输入高电平和最大输入低电平:输入高电平>=2.0V,输入低电平<=0.8V,噪声容限是0.4V。也就是说b模拟输入,是直接从io引入,并且与c数字部分进行了隔离.数字部分使用ttl电平的触发器进行了缓冲,这个缓冲有时候也被称为buff,但是buff并不全是触发器.触发器的延时在5-10ns之间.当然i和c会同时获取ttl肖特基触发器的输出,触发器也对信号的驱动能力进行了提高,至于是c还是d来消费掉这个信号,就看你io配置成什么功能了.

对于GPIO的o, output,就从左向右进行分析.首先是信号的生成,其一是寄存器,由cpu来操作.e和f共两种操作,e是单次操作只能设置寄存器的某些位为1,或者清除某些位为0,影响部分bit,而f是直接将输出寄存器改变,影响 全部bit.对于j是硬件控制器自动生成信号流,这里就不用详述了.控制输出前面的梯形是选择器,选择其中的一路有效.无效的一路cpu也可以操作.但是毫无意义.很多人都是在这个坑里出不来,我做了一些操作,但是io不听话.对于控制输出和m/n两个管子共同生成高低电平的切换.当然,这里会有一个死区控制.别看这芯片原理图这么画,就认为是这么简单设计.如果用桥电路控制电机就会掉坑里.因为图上的控制框是有死区控制的.并且能控制好.控制不好就会出现跳变的时候io功率很大.对于电机桥电路来说.就是直接烧坏驱动芯片.做输出的时候,上下拉电阻都是断开的.但是保护二极管没有断开.这里提出一个问题,虽然是输出,信号会过充吗?大家自己去考虑.

写道这里,图解gpio就结束了.把中间的两个复杂的问题总结一下答案.

1. 振铃信号 2.gpio的频率

振铃信号是因为电路的阻抗匹配出问题导致.也就是信号线上的电感和电容导致了信号的震荡.这个震荡与信号的跳变间隔基本无关.但跳变间隔长的信号,对振铃不敏感而已.因为他们有更多的采样时间.在工业级总线上可以多次采样求平均值来扛干扰.震荡信号与跳变的边沿有关.跳变边沿的频率约为信号反转频率的10倍.就是一个1k的串口信号,跳变频率大约在10k级别.所以2.gpio的频率是1振铃信号的产生原因之一.既然是之一,那么,就可以通过修改它来减少振铃信号.提高信号的稳定程度.并且减少干扰.那么对于小于200K的时钟来说,设置2M时钟即可.对于小于1M的信号,设置10M输出即可.对于5M以下的信号,设置50Mhz,对于5M以上的信号,也只能设置50Mhz,这时候,你要去考虑信号边沿的斜率是不是能满足你的需要了.例如io频率在48M的时候,波形可能已经不是漂亮的方波了.但是不代表这个信号是不能用的.要看你的接收方是不是认可这种信号.当然,这里我也不用多说了,遇到这种问题的人,都知道如何解决.只不过没法找到万能的解决办法.