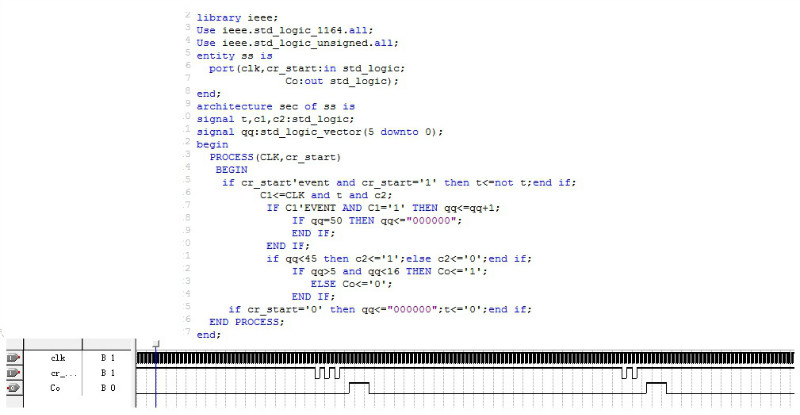

锁定一段时间的及时程序:

library ieee;

Use ieee.std_logic_1164.all;

Use ieee.std_logic_unsigned.all;

entity ss is

port(clk,cr_start:in std_logic;

Co:out std_logic);

end;

architecture sec of ss is

signal t,c1,c2:std_logic;

signal qq:std_logic_vector(5 downto 0);

begin

PROCESS(CLK,cr_start)

BEGIN

if cr_start'event and cr_start='1' then t<=not t;end if;

C1<=CLK and t and c2;

IF C1'EVENT AND C1='1' THEN qq<=qq+1;

IF qq=50 THEN qq<="000000";

END IF;

END IF;

if qq<45 then c2<='1';else c2<='0';end if;

IF qq>5 and qq<16 THEN Co<='1';

ELSE Co<='0';

END IF;

if cr_start='0' then qq<="000000";t<='0';end if;

END PROCESS;

end;

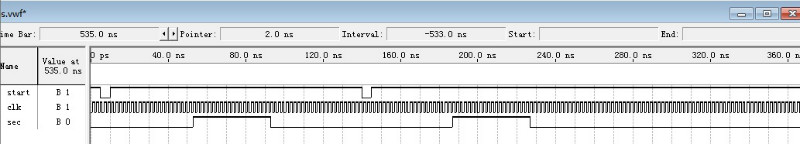

下面是波形仿真:按一下开始键可以从新开始这段计时。

以下是在上面锁定一段时间后编写的频率计程序:

library ieee;

Use ieee.std_logic_1164.all;

Use ieee.std_logic_unsigned.all;

entity plj is

port(cp,cr_start,Dce:in std_logic;

xs:out std_logic_vector(6 downto 0);

w:out std_logic_vector(5 downto 0);

Co:out std_logic);

end;

architecture sec of plj is

signal t,c1,c2,clk,sec,cc:std_logic;

signal qq:std_logic_vector(5 downto 0);

signal q:std_logic_vector(19 downto 0);

signal q0,q1,q2,q3,q4,q5,XSQ:std_logic_vector(3 downto 0);

signal tt:std_logic_vector(9 downto 0);

begin

process(cp)

begin

if cp'event and cp='1' then q<=q+1;tt<=tt+1;

if q<=999999 then q<="00000000000000000000";clk<='1';

else clk<='0';

end if;

if tt=769 then tt<="0000000000";end if;

end if;

end process;

PROCESS(CLK,cr_start,Dce)

BEGIN

if cr_start'event and cr_start='1' then t<=not t;end if;

C1<=CLK and t and c2;

IF C1'EVENT AND C1='1' THEN qq<=qq+1;

IF qq=50 THEN qq<="000000";

END IF;

END IF;

if qq<45 then c2<='1';else c2<='0';end if;

IF qq>5 and qq<26 THEN sec<='1';

ELSE sec<='0';

END IF;

----------------------开始测试频率----------------------------------

cc<= Dce and sec ;

if cc'event and cc='1' then q0<=q0+1;

if q0=9 then q0<="0000";q1<=q1+1;end if;

if q1=9 and q0=9 then q1<="0000";q2<=q2+1;end if;

if q2=9 and q1=9 and q0=9 then q2<="0000";q3<=q3+1;end if;

if q3=9 and q2=9 and q1=9 and q0=9 then q3<="0000";q4<=q4+1;end if;

if q4=9 and q3=9 and q2=9 and q1=9 and q0=9 then q4<="0000";q5<=q5+1;end if;

if q5>9 then q0<="1111";q1<="1111";q2<="1111";q3<="1111";q4<="1111";q5<="1111";end if;

end if;

if tt<128 then XSQ<=q0;w<="111110";end if;

if tt>=128 and tt<256 then XSQ<=q1;w<="111101";end if;

if tt>=256 and tt<384 then XSQ<=q2;w<="111011";end if;

if tt>=384 and tt<512 then XSQ<=q1;w<="111101";end if;

if tt>=512 and tt<640 then XSQ<=q2;w<="111011";end if;

if tt>=640 and tt<768 then XSQ<=q2;w<="111011";end if;

if cr_start='0' then qq<="000000";t<='0';q0<="0000";q1<="0000";

q2<="0000"; q3<="0000"; q4<="0000"; q5<="0000";

end if;

END PROCESS;

----------------------开始显示----------------------------------

process(XSQ)

begin

case XSQ is

when "0000"=>XS<="0000001";

when "0001"=>XS<="1001111";

when "0010"=>XS<="0010010";

when "0011"=>XS<="0000110";

when "0100"=>XS<="1001100";

when "0101"=>XS<="0100100";

when "0110"=>XS<="0100000";

when "0111"=>XS<="0001111";

when "1000"=>XS<="0000000";

when "1001"=>XS<="0000100";

when "1111"=>XS<="1111110";

when others=>XS<="0000001";

end case;

end process;--显示结束

end;

==============下面是六位十进制计数器========

if clk'event and clk='1' then bq0<=bq0+1;

if bq0=9 then bq0<="0000";bq1<=bq1+1;end if;

if bq1=5 and bq0=9 then bq1<="0000";bq2<=bq2+1;end if;

if bq2=9 and bq1=5 and bq0=9 then bq2<="0000";bq3<=bq3+1; end if;

if bq3=5 and bq2=9 and bq1=5 and bq0=9 then bq3<="0000";bq4<=bq4+1;end if;

if bq4=9 and bq3=5 and bq2=9 and bq1=5 and bq0=9 then bq4<="0000";bq5<=bq5+1;end if;

if bq5=2 and bq4=3 and bq3=5 and bq2=9 and bq1=5 and bq0=9 then bq4<="0000";bq5<="0000"; end if;

end if;

=====================================

-----------将20M分频成20Hz-----------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity fpq is

port( clk:in std_logic;

cp:out std_logic);

end;

architecture ss of fpq is

signal q:std_logic_vector(23 downto 0);

signal c:std_logic;

begin

process(clk)

begin

if clk'event and clk='1' then q<=q+1;

if q=499999 then c<=not c;end if;

end if;

end process;

cp<=c;

end;

------------------产生1秒种的计数时间------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity sec_1s is

port( clk,start:in std_logic;

sec:out std_logic);

end;

architecture ss of sec_1s is

signal q:std_logic_vector(5 downto 0);

signal c0,c1,c2:std_logic;

begin

process(clk,start)

begin

if start'event and start='1' then c0<=not c0;end if;

c2<=clk and c0 and (not c1);

if c2'event and c2='1' then q<=q+1;

if q>51 then c1<='1';else c1<='0';end if;

if q>20 and q<41 then sec<='1';else sec<='0';end if;

end if;

if start='0' then c0<='0';q<="000000";c1<='0';end if;

end process;

end;

-----------------测试待测频率------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity plvcs is

port( sec1s,start,daice_f:in std_logic;

q0,q1,q2,q3,q4,q5:out std_logic_vector(3 downto 0));

end;

architecture ss of plvcs is

signal qq0,qq1,qq2,qq3,qq4,qq5:std_logic_vector(3 downto 0);

signal cp:std_logic;

begin

process(sec1s,start,daice_f)

begin

cp<=sec1s and daice_f;

if cp'event and cp='1' then qq0<=qq0+1;

if qq0=9 then qq0<="0000";qq1<=qq1+1;end if;

if qq0=9 and qq1=9 then qq1<="0000";qq2<=qq2+1;end if;

if qq0=9 and qq1=9 and qq2=9 then qq2<="0000";qq3<=qq3+1;end if;

if qq0=9 and qq1=9 and qq2=9 and qq3=9 then qq3<="0000";qq4<=qq4+1;end if;

if qq0=9 and qq1=9 and qq2=9 and qq3=9 and qq4=9 then qq4<="0000";qq5<=qq5+1;end if;

if qq5>9 then qq4<="1111";qq5<="1111";qq3<="1111";qq2<="1111";qq1<="1111";qq0<="1111";end if;

end if;

if start='0' then qq4<="0000";qq5<="0000";qq3<="0000";qq2<="0000";qq1<="0000";qq0<="0000";end if;

end process;

q0<=qq0;q1<=qq1;q2<=qq2;q3<=qq3;q4<=qq4;q5<=qq5;

end;

-------------七段码显示测试结果-----------------------------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity xs is

port(clk:in std_logic;

q0,q1,q2,q3,q4,q5:in std_logic_vector(3 downto 0);

xs:out std_logic_vector(6 downto 0);

w:out std_logic_vector(5 downto 0));

end;

architecture ss of xs is

signal q:std_logic_vector(5 downto 0);

signal qq:std_logic_vector(3 downto 0);

begin

process(q0,q1,q2,q3,q4,q5,clk)

begin

if clk'event and clk='1' then q<=q+1;

if q=59 then q<="000000";end if;

end if;

if q<10 then qq<=q0;w<="111110";end if;

if q>=10 and q<20 then qq<=q1;w<="111101";end if;

if q>=20 and q<30 then qq<=q2;w<="111011";end if;

if q>=30 and q<40 then qq<=q3;w<="110111";end if;

if q>=40 and q<50 then qq<=q4;w<="101111";end if;

if q>=50 then qq<=q5;w<="011111";end if;

case qq is

when "0000"=>xs<="0000001";

when "0001"=>xs<="1001111";

when "0010"=>xs<="0010010";

when "0011"=>xs<="0000110";

when "0100"=>xs<="1001100";

when "0101"=>xs<="0100100";

when "0110"=>xs<="0100000";

when "0111"=>xs<="0001111";

when "1000"=>xs<="0000000";

when "1001"=>xs<="0000100";

when "1111"=>xs<="1111110";

when others=>xs<=null;

end case;

end process;

end;

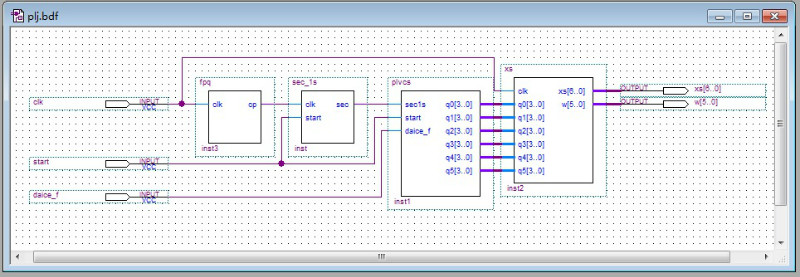

---------------------------原理图完成频率计整体测试-----------------------------

FPGA频率计带注释的VHDL程序

【关闭窗口】

上一篇:在VHDL中实现高精度快速除法

下一篇:FPGA流星雨灯的VHDL程序