记得某位网友曾经说过,学习任何一款单片机,首先要学的是它的时钟。的确如此,时钟是如此的重要,在不知道系统时钟的情况,感觉做什么事都是迷迷糊糊的。

之前学过51,它的时钟很简单,就一个外部晶振。然后学了430的G2553,它的时钟就有点麻烦了,时钟源多(两个外部晶振,一个内部超低功耗低频振荡器,一个内部调整低频参考振荡器),内部还有锁频环,而且出来的时钟还能被分频。原因是TI主打低功耗,必须得有各种频率来满足设计需要,毕竟,频率越低,功耗越低。

现在的,430的F5529,跟G2553比起来也就需要配置的时钟相关的寄存器是其3倍而已…还有个PMM(电源管理模块)的配置…

新增的PMM是干嘛的呢?还是那句话,TI主打超低功耗。PMM不仅完成了对电源的监管和监测(这五个字包含了太多的内容…能力有限,不多解释),还为用户提供了更改核心电压(VCORE)的途径。都知道,作为一个系统,肯定要供电的,5529有宽的电源(DVCC)电压范围1.8V-3.6V。DVCC经低压降电压调整器(LDO),产生的一个二次核心电压,专门为CPU数字逻辑供电,共有1.4V(0-12MHZ),1.6V(0-16MHZ),1.8V(0-20MHZ)和1.9V(0-25MHZ)四个级别。当系统需要的时钟频率不高时,我们可以配置低的时钟,可以配置低的VCORE,这样在时钟方面就把功耗降到最低了。当然,函数库HAL_PMM.c/h中有SetVCore(uint8_t level) ,轻轻松松地就可以设置VCORE了。

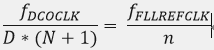

那下面就是真正的时钟配置了。学过数字逻辑电路的,对分频应该很熟悉。那倍频呢?锁频环(FLL)到底是什么?还有经常被提到的锁相环(PLL)又是什么?往往打败新手的都是一些陌生的名词。锁频环,顾名思义,就是使两个信号的频率能达到某种关系。而这两个信号,一个可以是输入时钟的子信号(刚刚说了,分频很容易实现的),另一个可以是输出时钟的子信号。现在再看看文档给出的公式:

当D*(N + 1)越大的时候,fDCOCLK也就越大了,从而也就达到了倍频的作用啦!锁相环的原理也是类似咯,把两个信号的相位锁定相等了,那频率也就相等了,而这两个信号同样是输入和输出时钟的子信号,而且都是它们的分频。至于怎么锁频,如何锁相,有数字鉴频器,数字鉴相器,再加上反馈(说起来简单,是因为我懂的不多…)。

1.

2.

3.

4.

5.

6.