一、 设计目标要求:

【1】 具有“时”、“分”、“秒”计时功能能;

【2】 能进行24|12小时计时模式切换;

【3】 具有校时和清除功能,能够对“小时”和“分”进行调整;

【4】 具有整点报时功能。在59分51秒、53秒、55秒、57秒发出低音1024Hz信号,在59分59秒发出一次高音2048Hz信号,音响持续1秒钟,在2048Hz音响结束时刻为整点。

二、 设计原理及效果:

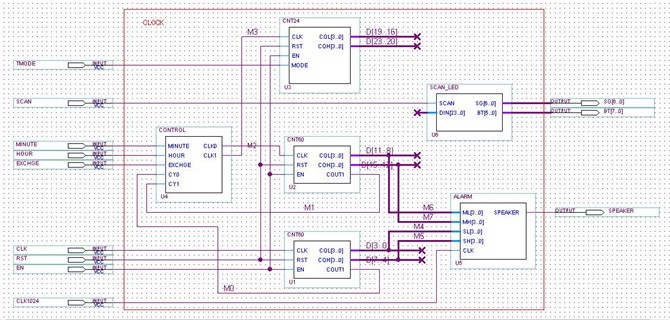

【1】电路原理图:

【2】设计简要说明:

本设计在实验箱上验证,使用电路模式7,用动态扫描方式显示,“DS8使能”开关上推;动态位扫描时,时、分、秒之间间隔点亮;

TMODE:12/24进制模式切换,接键8;

SCAN:动态扫描时钟信号,接CLOCK0,跳线选16384Hz;

MINUTE:分校时,接键1(单脉冲);

HOUR:小时时校时,接键4(单脉冲);

EXCHGE:计时/校时切换,接键5;

CLK::时钟脉冲,接CLOCK2,跳线选1Hz;

RET:清零,接键7(单脉冲);

EN:计数使能,接键3;

CLK1024:蜂鸣输入信号,接CLOCK5,跳线选1024Hz;

SG[6..0]:段选信号,接PIO49到PIO43;

BT[7..0]:位选信号,接PIO41到PIO34;

SPEAKER:蜂鸣输出信号,接SPEAKER。

【3】实验效果:

【1】60进制模块——CNT60

LIBRARY IEEE; --------CLK时钟输入,RET清零,EN计数使能,

USE IEEE.STD_LOGIC_1164.ALL; -------- CQL分或秒的个位输出,

USE IEEE.STD_LOGIC_UNSIGNED.ALL; --------CQH分或秒的十位输出,

ENTITY CNT60 IS -------- COUT1进位输出

PORT (CLK,RST,EN : IN STD_LOGIC;

CQL: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

CQH: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

COUT1 : OUT STD_LOGIC); --------向外部的进位

END CNT60;

ARCHITECTURE behav OF CNT60 IS

SIGNAL CQI0: STD_LOGIC_VECTOR (3 DOWNTO 0);

SIGNAL CQI1: STD_LOGIC_VECTOR (3 DOWNTO 0);

SIGNAL COUT0 : STD_LOGIC; ------低位向高位的进位

BEGIN

PROCESS(CLK,RST,EN) -------十进制

BEGIN

IF RST='1' THEN CQI0 <=(OTHERS =>'0');

ELSIF CLK'EVENT AND CLK='1' THEN

IF EN ='1' THEN

IF CQI0 <9 THEN CQI0 <=CQI0+1;

ELSE CQI0 <=(OTHERS=>'0');

END IF;

END IF;

IF CQI0 = 9 THEN COUT0 <= '1';

ELSE COUT0<='0';

END IF;

END IF;

END PROCESS;

CQL<=CQI0;

PROCESS(COUT0,RST) ------六进制

BEGIN

IF RST='1' THEN CQI1 <=(OTHERS =>'0');

ELSIF COUT0'EVENT AND COUT0='1' THEN

IF CQI1<5 THEN CQI1<=CQI1+1;

ELSE CQI1<=(OTHERS=>'0');

END IF;

IF CQI1=5 AND CQI0=9 THEN COUT1<='1';

ELSE COUT1<='0';

END IF;

END IF;

END PROCESS;

CQH<=CQI1;

END behav;

【2】24|12进制模块——CNT24

LIBRARY IEEE; ---------CLK输入分的进位信号,RET清零,EN计数使能,

USE IEEE.STD_LOGIC_1164.ALL; ----------MODE为12和24进制的切换,

USE IEEE.STD_LOGIC_UNSIGNED.ALL; --------- CQL小时的个位输出,CQH小时的十位输出

ENTITY CNT24 IS

PORT (CLK,RST,EN,MODE: IN STD_LOGIC;

CQL: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

CQH: OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END CNT24;

ARCHITECTURE behav OF CNT24 IS

SIGNAL CQI0: STD_LOGIC_VECTOR (3 DOWNTO 0);

SIGNAL CQI1: STD_LOGIC_VECTOR (3 DOWNTO 0);

SIGNAL CQI2: STD_LOGIC_VECTOR (3 DOWNTO 0);

SIGNAL CQI3: STD_LOGIC_VECTOR (3 DOWNTO 0);

BEGIN

P1: PROCESS(CLK,RST,EN) --------24进制模式

BEGIN

IF RST='1' THEN

CQI0 <=(OTHERS =>'0');CQI1 <=(OTHERS =>'0');

ELSIF CLK'EVENT AND CLK='1' THEN

IF EN ='1' THEN

IF CQI1<2 THEN

IF CQI0<9 THEN

CQI0<=CQI0+1;

ELSE CQI0<=(OTHERS=>'0');

CQI1<=CQI1+1;

END IF;

ELSIF CQI0<3 THEN

CQI0<=CQI0+1;

ELSE CQI0<=(OTHERS=>'0');

CQI1<=(OTHERS=>'0');

END IF;

END IF;

END IF;

END PROCESS P1;

P2: PROCESS(CLK,RST,EN) ------12进制模式

BEGIN

IF RST='1' THEN

CQI2 <=(OTHERS =>'0');CQI3 <=(OTHERS =>'0');

ELSIF CLK'EVENT AND CLK='1' THEN

IF EN ='1' THEN

IF CQI3<1 THEN

IF CQI2<9 THEN

CQI2<=CQI2+1;

ELSE CQI2<=(OTHERS=>'0');

CQI3<=CQI3+1;

END IF;

ELSIF CQI2<2 THEN

CQI2<=CQI2+1;

ELSE CQI2<="0001";

CQI3<=(OTHERS=>'0');

END IF;

END IF;

END IF;

END PROCESS P2;

P3: PROCESS(MODE) ------MODE=’1’为24进制,MODE=’0’为12进制

BEGIN

CASE MODE IS

WHEN '1'=> CQL<=CQI0;CQH<=CQI1;

WHEN '0'=> CQL<=CQI2;CQH<=CQI3;

WHEN OTHERS=>NULL;

END CASE;

END PROCESS P3;

END behav;

【3】控制逻辑模块——CONTROL

LIBRARY IEEE; -------EXCHGE校时与计时模式控制,

USE IEEE.STD_LOGIC_1164.ALL; -------MINUTE手动分校时

USE IEEE.STD_LOGIC_UNSIGNED.ALL; -------HOUR手动时校时

ENTITY CONTROL IS -------CY0,CY1分别接受秒和分的进位信号

PORT (MINUTE,HOUR,EXCHGE,CY0,CY1: IN STD_LOGIC; ------CLK0,CLK1分别控制分和小时的时钟脉冲

CLK0: OUT STD_LOGIC;

CLK1: OUT STD_LOGIC);

END CONTROL;

ARCHITECTURE behav OF CONTROL IS

SIGNAL A0: STD_LOGIC;

SIGNAL A1: STD_LOGIC;

BEGIN

P1: PROCESS(EXCHGE,MINUTE,HOUR)

BEGIN

IF EXCHGE='1' THEN

A0<=MINUTE;

A1<=HOUR;

END IF;

END PROCESS P1;

P2: PROCESS(EXCHGE,CY0,CY1) -------EXCHGE=’1’校时模式,EXCHGE=’0’为计时模式

BEGIN

IF EXCHGE='1' THEN

CLK0<=A0;CLK1<=A1;

ELSE CLK0<=CY0;CLK1<=CY1;

END IF;

END PROCESS P2;

END ARCHITECTURE behav;

【4】动态扫描模块——SCAN_LED

LIBRARY IEEE; -------SCAN动态扫描时钟信号

USE IEEE.STD_LOGIC_1164.ALL; -------DIN接受时、分、秒数据

USE IEEE.STD_LOGIC_UNSIGNED.ALL; -------SG输出段选信号

ENTITY SCAN_LED IS -------BT输出位选信号

PORT(SCAN : IN STD_LOGIC;

DIN:IN STD_LOGIC_VECTOR(23 DOWNTO 0);

SG:OUT STD_LOGIC_VECTOR(6 DOWNTO 0);

BT:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END;

ARCHITECTURE one OF SCAN_LED IS

SIGNAL CNT6:STD_LOGIC_VECTOR(2 DOWNTO 0);

SIGNAL D:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

P1:PROCESS(SCAN)

BEGIN

IF SCAN'EVENT AND SCAN='1' THEN

IF CNT6<5 THEN

CNT6<=CNT6+1;

ELSE CNT6<="000";

END IF;

END IF;

END PROCESS P1;

P2:PROCESS(CNT6) --------位选

BEGIN

CASE CNT6 IS

WHEN"000"=> BT <="00000001"; --------时、分、秒之间隔一个数码管显示

WHEN"001"=> BT <="00000010";

WHEN"010"=> BT <="00001000";

WHEN"011"=> BT <="00010000";

WHEN"100"=> BT <="01000000";

WHEN"101"=> BT <="10000000";

WHEN OTHERS => NULL;

END CASE;

END PROCESS P2;

P4: PROCESS(CNT6)

BEGIN

CASE CNT6 IS

WHEN"000"=> D <=DIN(3 DOWNTO 0);

WHEN"001"=> D <=DIN(7 DOWNTO 4);

WHEN"010"=> D <=DIN(11 DOWNTO 8);

WHEN"011"=> D <=DIN(15 DOWNTO 12);

WHEN"100"=> D <=DIN(19 DOWNTO 16);

WHEN"101"=> D <=DIN(23 DOWNTO 20);

WHEN OTHERS=>NULL;

END CASE;

END PROCESS P4;

P3:PROCESS(D) -------段选

BEGIN

CASE D IS

WHEN "0000" =>SG<="0111111";WHEN "0001" =>SG<="0000110";

WHEN "0010" =>SG<="1011011";WHEN "0011" =>SG<="1001111";

WHEN "0100" =>SG<="1100110";WHEN "0101"=>SG<="1101101";

WHEN "0110" =>SG<="1111101";WHEN "0111" =>SG<="0000111";

WHEN "1000" =>SG<="1111111";WHEN "1001" =>SG<="1101111";

WHEN OTHERS=>NULL;

END CASE;

END PROCESS P3;

END ARCHITECTURE one;

【5】整点报时模块——ALARM

LIBRARY IEEE; ------ML输入分个位,MH输入分十位

USE IEEE.STD_LOGIC_1164.ALL; ------SL输入秒个位,SH输入秒十位

USE IEEE.STD_LOGIC_UNSIGNED.ALL; ------CLK输入1024Hz时钟脉冲

ENTITY ALARM IS ------SPEAKER输出报时信号

PORT (ML: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

MH: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

SL: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

SH: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

CLK: IN STD_LOGIC;

SPEAKER: OUT STD_LOGIC);

END ALARM;

ARCHITECTURE behav OF ALARM IS

SIGNAL DIV2CLK: STD_LOGIC;

BEGIN

PROCESS(CLK)

BEGIN ----------实验箱的可用时钟有限,1024Hz作高音信号

IF CLK'EVENT AND CLK='1' THEN -----------1024Hz时钟脉冲2分频,产生蜂鸣低音信号

DIV2CLK<=NOT DIV2CLK;

END IF;

END PROCESS;

PROCESS(MH,ML,SH,SL)

BEGIN

IF MH=5 AND ML=9 THEN

IF SH=5 THEN

IF (SL=1 OR SL=3 OR SL=5 OR SL=7) THEN -------51、53、55、57秒输出低音信号

SPEAKER<=DIV2CLK;

ELSIF (SL=9) THEN --------59秒输出高音信号

SPEAKER<=CLK;

ELSE SPEAKER<='0';

END IF;

ELSE SPEAKER<='0';

END IF;

ELSE SPEAKER<='0';

END IF;

END PROCESS;

END ARCHITECTURE behav;

【6】顶层实体——CLOCK

LIBRARY IEEE; ------CLK接1Hz时钟脉冲,

USE IEEE.STD_LOGIC_1164.ALL; ------ RET接清零键,EN接计数使能键,

ENTITY CLOCK IS ------SCAN接CLK0时钟扫描信号

PORT(CLK,EN,RST,SCAN,TMODE,EXCHGE:IN STD_LOGIC; ------TMODE12|24进制切换

HOUR,MINUTE,CLK1024:IN STD_LOGIC; -------EXCHGE计时|校时模式控制

SPEAKER: OUT STD_LOGIC; -------HOUR手动时校时

SG:OUT STD_LOGIC_VECTOR(6 DOWNTO 0); -------MINUTE手动分校时

BT:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); ------CLK1024接1024Hz时钟脉冲

END ENTITY; -------SG输出段选信号

ARCHITECTURE STRUC OF CLOCK IS -------BT输出位选信号

COMPONENT CNT60 ------SPEAKER接蜂鸣器

PORT (CLK,RST,EN : IN STD_LOGIC;

CQL: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

CQH: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

COUT1 : OUT STD_LOGIC);

END COMPONENT;

COMPONENT CNT24

PORT (CLK,RST,EN,MODE: IN STD_LOGIC;

CQL: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

CQH: OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END COMPONENT;

COMPONENT CONTROL

PORT (MINUTE,HOUR,EXCHGE,CY0,CY1: IN STD_LOGIC;

CLK0: OUT STD_LOGIC;

CLK1: OUT STD_LOGIC);

END COMPONENT;

COMPONENT SCAN_LED

PORT(SCAN : IN STD_LOGIC;

DIN:IN STD_LOGIC_VECTOR(23 DOWNTO 0);

SG:OUT STD_LOGIC_VECTOR(6 DOWNTO 0);

BT:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END COMPONENT;

COMPONENT ALARM IS

PORT (ML: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

MH: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

SL: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

SH: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

CLK: IN STD_LOGIC;

SPEAKER: OUT STD_LOGIC);

END COMPONENT;

SIGNAL D :STD_LOGIC_VECTOR(23 DOWNTO 0);

SIGNAL M0,M1,M2,M3 :STD_LOGIC;

SIGNAL M4,M5,M6,M7 :STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

u1: CNT60 PORT MAP(CLK=>CLK,RST=>RST,EN=>EN,COUT1=>M0,

CQH=>D(7 DOWNTO 4),CQL=>D(3 DOWNTO 0));

u2: CNT60 PORT MAP(CLK=>M2,RST=>RST,EN=>EN,COUT1=>M1,

CQH=>D(15 DOWNTO 12),CQL=>D(11 DOWNTO 8));

u3: CNT24 PORT MAP(CLK=>M3,RST=>RST,EN=>EN,MODE=>TMODE,

CQH=>D(23 DOWNTO 20),CQL=>D(19 DOWNTO 16));

u4: CONTROL PORT MAP(EXCHGE=>EXCHGE,HOUR=>HOUR,MINUTE=>MINUTE,

CLK0=>M2,CLK1=>M3,CY0=>M0,CY1=>M1);

u5: SCAN_LED PORT MAP(SCAN=>SCAN,SG=>SG,BT=>BT,

DIN(3 DOWNTO 0)=>D(3 DOWNTO 0),

DIN(7 DOWNTO 4)=>D(7 DOWNTO 4),

DIN(11 DOWNTO 8)=>D(11 DOWNTO 8),

DIN(15 DOWNTO 12)=>D(15 DOWNTO 12),

DIN(19 DOWNTO 16)=>D(19 DOWNTO 16),

DIN(23 DOWNTO 20)=>D(23 DOWNTO 20));

U6: ALARM PORT MAP(ML=>M6,MH=>M7,SL=>M4,SH=>M5,CLK=>CLK1024,

SPEAKER=>SPEAKER);

END STRUC;