作为一个菜鸟我很愿意分享下我做的一些小东西,记得一年前好像少几天吧,看记录是2009年5月19日

我用51单片机做数字钟的情景,那个时候用汇编,焦头烂额,做了三天,还请教了老师。

哎,现在都已经用C了,而且重心已经放在了AVR上,

不过想想,这一年我还是学了很多东西,至少不是虚度了这一年。

FPGA是挺好玩的,不过没有时间搞,忙着比赛。

不过凭借着学期前两个礼拜实习天天晚上去图书馆自学VHDL的基础,加上单片机的基础,一直活到现在。呵呵呵

臭屁一下,今天老师说我可以做他的助教,确实把我兴奋了一把,

其实我一直很心虚,因为都没有时间搞,哪天出个难题答不上来就糗了。

今天中午和下午花了6个小时左右的时间做了一个数字钟,

VHDL语言(Very high speed integrated circuit Hardware Description Language)即超高速集成电路硬件描述语言。

顾名思义既然是硬件描述,当然是描述硬件,这个语言相当于在FPGA或CPLD芯片里熔出一个数字电路。

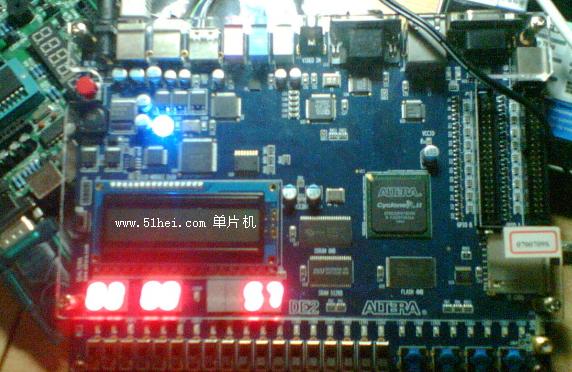

硬件FPGA 芯片是ALTERA公司Cyclone II 系列的EP2C35F672C6

使用的是ALTERA公司的开发板,型号DE2来张全图,软件为Quartus II 8.0,、ALTERA公司为自己产品打造的开发软件。

据说是5000块钱,因为是学校教学用,批量买,2500块钱(不过我看下,就芯片贵,我看这个板子人家至少赚了1000多),我原来以为老师不会借,不过他似乎不介意,倒是他主动借给我的,额。。。

不费话了,贴程序吧

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity fpq is

port(clk : in std_logic;

k : in std_logic;

k1 : in std_logic;

k2 : in std_logic;

ge : out std_logic_vector(0 to 6);

shi : out std_logic_vector(0 to 6);

feng : out std_logic_vector(0 to 6);

fens : out std_logic_vector(0 to 6);

shig : out std_logic_vector(0 to 6);

shis : out std_logic_vector(0 to 6));

end fpq;

architecture first of fpq is

signal clock : integer range 0 to 24999999;

signal ge_t : integer range 0 to 9;

signal shi_t : integer range 0 to 5;

signal feng_t : integer range 0 to 9;

signal fens_t : integer range 0 to 5;

signal shig_t : integer range 0 to 9;

signal shis_t : integer range 0 to 2;

signal temp : integer range 0 to 9;

begin

t0: process(clk)

begin

if (clk'event and clk='1') then

clock <= clock + 1;

if clock = 24999999 then

---------------------------------------------

if k='0' then

---------------------------------------------

if ge_t = 9 then

ge_t <= 0;

if shi_t = 5 and ge_t = 9 then

shi_t <= 0;

if feng_t = 9 and shi_t = 5 then

feng_t <= 0;

if fens_t = 5 and feng_t = 9 then

fens_t <= 0;

if shis_t = 2 and shig_t = 3 and fens_t = 5 then

shig_t <= 0;

if shis_t = 2 and shig_t = 3 then

shis_t <= 0;

else

shis_t <= shis_t + 1;

end if;

else

if shig_t = 9 and fens_t = 5 then

shig_t <= 0;

else

shig_t <= shig_t +1;

end if;

end if;

else

fens_t <= fens_t + 1;

end if;

else

feng_t <= feng_t + 1;

end if;

else

shi_t <= shi_t + 1;

end if;

else

ge_t <= ge_t + 1;

end if;

else

if k1='0' then

if feng_t = 9 then

feng_t <= 0;

if fens_t = 5 then

fens_t <= 0;

else

fens_t <= fens_t + 1;

end if;

else

feng_t <= feng_t + 1;

end if;

end if;

if k2='0' then

if shig_t = 3 and shis_t = 2 then

shig_t <= 0;

shis_t <= 0;

else

if shig_t = 9 then

shig_t <= 0;

if shis_t = 2 then

shis_t <= 0;

else

shis_t <= shis_t + 1;

end if;

else

shig_t <= shig_t + 1;

end if;

end if;

end if;

end if;

------------------------------------------------

end if;

end if;

------------------------------------------------

end process t0;

c: process(clk,ge_t,shi_t,feng_t,fens_t,shig_t,shis_t)

begin

case ge_t is

when 9 => ge <= "0000100";

when 8 => ge <= "0000000";

when 7 => ge <= "0001111";

when 6 => ge <= "0100000";

when 5 => ge <= "0100100";

when 4 => ge <= "1001100";

when 3 => ge <= "0000110";

when 2 => ge <= "0010010";

when 1 => ge <= "1001111";

when 0 => ge <= "0000001";

end case;

case shi_t is

when 5 => shi <= "0100100";

when 4 => shi <= "1001100";

when 3 => shi <= "0000110";

when 2 => shi <= "0010010";

when 1 => shi <= "1001111";

when 0 => shi <= "0000001";

end case;

case feng_t is

when 9 => feng <= "0000100";

when 8 => feng <= "0000000";

when 7 => feng <= "0001111";

when 6 => feng <= "0100000";

when 5 => feng <= "0100100";

when 4 => feng <= "1001100";

when 3 => feng <= "0000110";

when 2 => feng <= "0010010";

when 1 => feng <= "1001111";

when 0 => feng <= "0000001";

end case;

case fens_t is

when 5 => fens <= "0100100";

when 4 => fens <= "1001100";

when 3 => fens <= "0000110";

when 2 => fens <= "0010010";

when 1 => fens <= "1001111";

when 0 => fens <= "0000001";

end case;

case shig_t is

when 9 => shig <= "0000100";

when 8 => shig <= "0000000";

when 7 => shig <= "0001111";

when 6 => shig <= "0100000";

when 5 => shig <= "0100100";

when 4 => shig <= "1001100";

when 3 => shig <= "0000110";

when 2 => shig <= "0010010";

when 1 => shig <= "1001111";

when 0 => shig <= "0000001";

end case;

case shis_t is

when 2 => shis <= "0010010";

when 1 => shis <= "1001111";

when 0 => shis <= "0000001";

end case;

end process c;

end first;

和汇编有的一拼啊,呵呵,由于是新手,所以很多程序都带有单片机的想法,其实VHDL和C、FPGA和单片机是两种不同的语言、芯片,主要是要有并行思想和状态机的概念,很遗憾我现在好像都没有。

设置模式开关是sw01.、分钟设置按钮key01、key02 。

视频地址:http://v.youku.com/v_show/id_XMTcxMTMzODYw.html 不过很糊啊。。悲剧。

后记:臭屁一下