复位

有三种复位:系统复位、电源复位和后备域复位

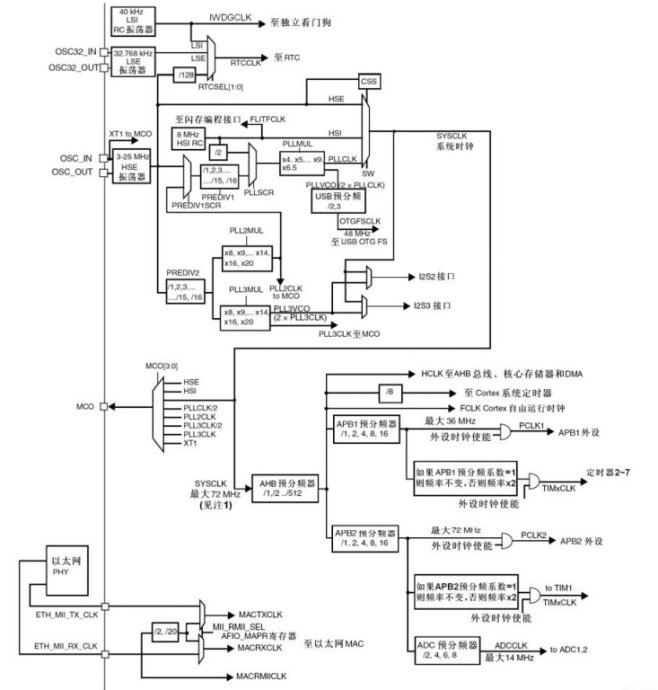

时钟

三种不同的时钟源可被用来驱动系统时钟(SYSCLK)

● HSI振荡器时钟

● HSE振荡器时钟

● PLL 时钟

这些设备有以下2种二级时钟源:

● 40kHz 低速内部RC(LSI RC)振荡器,可以用于驱动独立看门狗,或通过程序选择驱动RTC,用于从停机/ 待机 模式下自动唤醒系统。

● 也可以通过程序选择32.768kHz 低速外部晶体(LSE晶体)用来驱动RTC(RTCCLK)。

当不被使用时,任一个时钟源都可被独立地启动或关闭,由此优化系统功耗。

从下图看出有:

LSI(40KHz的内部低速时钟)

LSE(32.768KHz的外部时钟)

HSE (3-25M的外部输入高速时钟)

HSI (8M的内部高速时钟)

系统时钟SYSCLK经过AHB分频后可以直接给AHB、DMA等用,或者再经过APB1或APB2的分频再给外设使用。

除去以下情况,所有外设的时钟都是从系统时钟(SYSCLK) 得到:

● Flash存储器编程接口时钟始终是HSI时钟

● 全速USB OTG的48MHz时钟是从PCC VCO时钟(2xPLLCLK) ,和随后可编程预分频器(除3或除2) 得到,这是通 过RCC_CFGR寄存器的OTGFSPRE位控制。为了正常地操作USB全速OTG,应该配置PLL 输出72MHz或48MHz。

● 全速USB OTG的48MHz时钟是从PCC VCO时钟(2xPLLCLK) ,和随后可编程预分频器(除3或除2) 得到,这是通 过RCC_CFGR寄存器的OTGFSPRE位控制。为了正常地操作USB全速OTG,应该配置PLL 输出72MHz或48MHz。

● I2S2和I2S3的时钟还可以从PLL3 VCO 时钟(2xPLL3CLK)得到,这是通过RCC_CFGR2寄存器的I2SxSRC位制。 更多有关PLL3的内容和如何配置I2S 时钟,以得到高质量的音频效果,请参阅第23.4.381/754 节:时钟发 生器。

● 以太网MAC的时钟(TX 、RX和RMII)是由外部PHY提供。更多有关以太网配置的详情,请见

第27.4.4 MII/RMII的选择 节: 。

当使用以太网模块时,AHB时钟频率必须至少为25MHz。

RCC通过AHB时钟(HCLK)8 分频后作为Cortex 系统定时器(SysTick)的外部时钟。通过对SysTick控制与状态寄存器的设置,可选择上述时钟或Cortex(HCLK)时钟作为SysTick时钟。ADC时钟由高速APB2时钟经2、4 、6或8分频后获得。 定时器时钟频率分配由硬件按以下2种情况自动设置:

1. 如果相应的APB预分频系数是1,定时器的时钟频率与所在APB 总线频率一致。

2. 否则,定时器的时钟频率被设为与其相连的APB 总线频率的2倍。

FCLK是Cortex??-M3的自由运行时钟。

HSE时钟

高速外部时钟信号(HSE) 由以下两种时钟源产生:

● HSE外部晶体/ 陶瓷谐振器

● HSE用户外部时钟

为了减少时钟输出的失真和缩短启动稳定时间,晶体/ 陶瓷谐振器和负载电容器必须尽可能地靠近振荡器引脚。负载电容值必须根据所选择的振荡器来调整。

HSI时钟

HSI时钟信号由内部8MHz 的RC振荡器产生,可直接作为系统时钟或在2分频后作为PLL 输入。 HSI RC振荡器能够在不需要任何外部器件的条件下提供系统时钟。它的启动时间比HSE晶体振荡器短。然而,即使在校准之后它的时钟频率精度仍较差。

PLL

主PLL 以下述时钟源之一为输入,产生倍频的输出:

● HSI时钟除以2

● HSE或通过一个可配置分频器的PLL2时钟

LSE 时钟

LSE 晶体是一个32.768kHz 的低速外部晶体或陶瓷谐振器。它为实时时钟或者其他定时功能提供

一个低功耗且精确的时钟源。

LSI时钟

系统时钟(SYSCLK) 选择

/////////////////////////////////////

寄存器介绍 0x4002 1000 - 0x4002 13FF 复位和时钟控制(RCC)

时钟控制寄存器(RCC_CR) -->内外部各种时钟的使能,各个PLL的使能等

时钟配置寄存器(RCC_CFGR)-->配置各个时钟的分频系数以及PLL的分配系数以及时钟源的选择等

时钟配置寄存器(RCC_CFGR2)-->配置各个时钟的分频系数以及PLL的分配系数以及时钟源的选择等