|

|

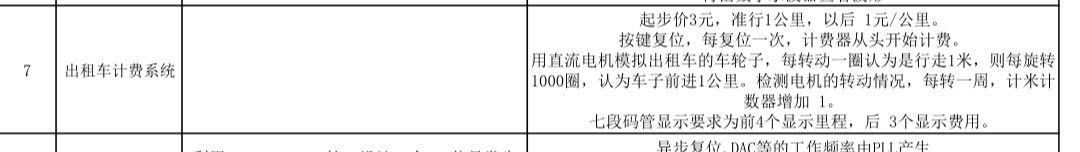

需要设计一个出租车计费系统,使用的DE1—soc实验箱,芯片为cyclone V

我在pwm控制直流电机处加了个计数(标红部分),下面代码能实现直流电机转一圈加1吗,求求大佬指导怎样可以让电机的里程与车费匹配,显示在数码管中,数码管不是一米一米的加。求求了!

基于quartusii的出租车计费器设计 试验箱芯片为cyclone V是DE1—SOC开发板的EDA实验箱,要求为1.2.1 里程与车费的准确计数:起步价为3元,以后1元每公里,并通过数码管显示,前四个数码管显示里程,后3个显示车费。1.2.2 直流电机旋转模拟车轮的转动:每转动一圈认为行走1米,每转1000圈认为车子前进1公里。1.2.3 综合:直流电机每转一圈,计里程的计数器要加1

要求

顶层例化

module w(clk,rst,key_in1,out1,out2,out3,out4,out5,out6,sctrl);

input clk,rst;

input key_in1;

output [6:0]out1,out2,out3,out4,out5,out6;

output sctrl;

wire key_out;

wire [6:0]count;

wire [6:0]PERCENT;

wire [6:0]fee;

xiaodou inst1(clk,rst,key_in1,key_out);

pwm inst2(clk,rst,PERCENT,count,sctrl);

speed inst3(clk,rst,key_out,PERCENT);

jifei inst4(count,rst,fee);

smg inst5(count,out1,out2,out3);

smg inst6(fee,out4,out5,out6);

endmodule

pwm控制直流电机

module pwm

(

input clk,

input rst,

input [6:0]PERCENT,

output reg [6:0]count,

output sctrl

);

parameter CYCLE = 50;

reg pwm_1;

reg [7:0] cnt_T;

always@(posedge clk or negedge rst)begin

if (!rst)

begin

cnt_T <= 0;

count<=0;

end

else if(cnt_T == CYCLE-1'b1)

begin

cnt_T <= 0;

count<=count+1'b1;

end

else

cnt_T <= cnt_T +1'b1;

end

always@(posedge clk or negedge rst)begin

if(!rst)

pwm_1 <= 0;

else if (cnt_T <= CYCLE * PERCENT /100 -1 )

pwm_1 <= 1;

else

pwm_1 <= 0;

end

assign sctrl=pwm_1;

endmodule

pwm占空比

module speed(clk,rst,key_out,PERCENT);

input clk,rst,key_out;

output reg [6:0]PERCENT;

always@(posedge clk or negedge rst)

begin

if(!rst)

PERCENT<=7'd5;

else if(key_out)

PERCENT<=7'd25;

end

endmodule

消抖

odule xiaodou(clk,rst,key_in1,key_out);

input clk,rst,key_in1;

output key_out;

reg key_value;

reg key_flag;

parameter CNT_20MS=32'd1_000_000;

reg [31:0] cnt_delay;

reg key_reg;

always@(posedge clk or negedge rst)begin

if (!rst)begin

cnt_delay<=32'd0;

key_reg<=1'b1;

end

else begin

key_reg<=key_in1;

if(key_reg!=key_in1)

cnt_delay<=CNT_20MS;

else begin

if (cnt_delay>32'd0)

cnt_delay<=cnt_delay-1'b1;

else

cnt_delay<=cnt_delay;

end

end

end

always @(posedge clk or negedge rst)begin

if(!rst)begin

key_value<=1'b1;

key_flag<=1'b0;

end

else begin

if (cnt_delay==32'd1)begin

key_value<=key_in1;

key_flag<=1'b1;

end

else begin

key_value<=key_value;

key_flag<=1'b0;

end

end

end

assign key_out=key_flag && (~key_value);

endmodule

计费

module jifei(count,rst,fee);

input [6:0]count;

input rst;

output reg [6:0]fee;

always@(*)

if(!rst)

fee<=7'd0;

else

fee<=7'd3+(count-7'd1)*7'd1;

endmodule

数码管显示

module smg(data,out1,out2,out3);

input [6:0]data;

output reg [6:0] out1,out2,out3;

always @(*)

begin

case(data%10)

7'd0: out1<=7'b1000000;

7'd1: out1<=7'b1111001;

7'd2: out1<=7'b0100100;

7'd3: out1<= 7'b0110000;

7'd4: out1<= 7'b0011001;

7'd5: out1<= 7'b0010010;

7'd6: out1<= 7'b0000010;

7'd7: out1<= 7'b1111000;

7'd8: out1<= 7'b0000000;

7'd9: out1<= 7'b0010000;

default:out1<=7'b0000000;

endcase

end

always@(*)

begin

case (data%100/10)

7'd0 : out2<= 7'b1000000;

7'd1 : out2 <= 7'b1111001;

7'd2 : out2 <= 7'b0100100;

7'd3 : out2 <= 7'b0110000;

7'd4 : out2<= 7'b0011001;

7'd5 : out2<= 7'b0010010;

7'd6 : out2 <= 7'b0000010;

7'd7 : out2 <= 7'b1111000;

7'd8 : out2 <= 7'b0000000;

7'd9 : out2<= 7'b0010000;

default : out2 <= 7'b0000000;

endcase

end

always @(*)

begin

case(data/100)

7'd0: out3<=7'b1000000;

7'd1: out3<=7'b1111001;

7'd2: out3<=7'b0100100;

7'd3: out3<= 7'b0110000;

7'd4: out3<= 7'b0011001;

7'd5: out3<= 7'b0010010;

7'd6: out3<= 7'b0000010;

7'd7: out3<= 7'b1111000;

7'd8: out3<= 7'b0000000;

7'd9: out3<= 7'b0010000;

default:out3<=7'b0000000;

endcase

end

endmodule

|

|