|

|

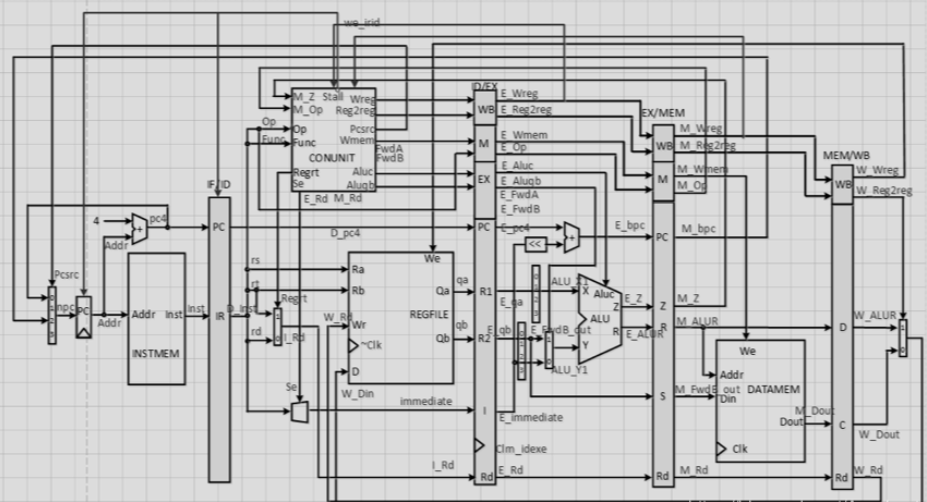

本文提供了一个基于FPGA的五级流水线CPU的设计代码。设计框图如下

- `timescale 1ns / 1ps

- `include "define.v"

- module openmips_min_sopc(

- input wire clk,

- input wire rst

- );

-

- wire [`InstAddrBus] inst_addr;

- wire [`InstBus] inst;

- wire rom_ce;

-

- wire mem_we_i;

- wire[`RegBus] mem_addr_i;

- wire[`RegBus] mem_data_i;

- wire[`RegBus] mem_data_o;

- wire[3:0] mem_sel_i;

- wire mem_ce_i;

-

- //例化c处理器openMiPs

- openmips openmips1(

- .clk(clk), .rst(rst),

- .rom_addr_o(inst_addr),

- .rom_data_i(inst),

- .rom_ce_o(rom_ce),

-

- .ram_we_o(mem_we_i),

- .ram_addr_o(mem_addr_i),

- .ram_sel_o(mem_sel_i),

- .ram_data_o(mem_data_i),

- .ram_data_i(mem_data_o),

- .ram_ce_o(mem_ce_i)

- );

-

- inst_rom inst_rom1(

- .ce(rom_ce), .addr(inst_addr),

- .inst(inst));

-

- data_ram data_ram0(

- .clk(clk),

- .we(mem_we_i),

- .addr(mem_addr_i),

- ……………………

- …………限于本文篇幅 余下代码请从51黑下载附件…………

|

-

-

-

代码.rar

1.82 KB, 下载次数: 19, 下载积分: 黑币 -5

|