eda万年历,可以显示年份,星期,时间,秒表计时等功能。文件夹包含论文,pcb板设计,quartus程序。

全部资料51hei下载地址:

system_test.rar

(6.89 MB, 下载次数: 133)

system_test.rar

(6.89 MB, 下载次数: 133)

formal_code.rar

(7.03 MB, 下载次数: 90)

formal_code.rar

(7.03 MB, 下载次数: 90)

FPGA万年历.docx

(1.7 MB, 下载次数: 99)

FPGA万年历.docx

(1.7 MB, 下载次数: 99)

pcb.rar

(645.2 KB, 下载次数: 58)

pcb.rar

(645.2 KB, 下载次数: 58)

基于FPGA的电子钟设计,主要完成的任务是使用Verilog语音,在Quartise2上完成电路的设计,程序的开发,基本功能是能够显示、修改年月日时分秒。电路的设计模块分为几个模块:分频、控制、时间显示调整、时分、年月日、译码器。各个模块完成不同的任务,合在一起就构成了电子钟。至于程序编写,使用Verilog语言,根据各个模块的不同功能和它们之间的控制关系进行编写。软件模块直接在Quartis2上进行。进入信息时代,时间观念越来越强,但是老是的钟表以及日历等时间显示工具已经不太合适。如钟表易坏,需经常维修,日历每天都需要翻页等。对此,数字钟表的设计就用了用武之地。 基于FPGA的电子钟设计,采用软件开发模块,开发成本底,而且功能设计上有很大的灵活度,需要在软件上进行简单的修该就能实现不同的功能要求,能够满足不同的环境要求。同时,该设计在精度上远远超过钟表,并且不需要维修,也不用每天的翻页,极其的方便。且能够添加各种不同的功能要求。例如:在其上加闹钟,同时显示阴阳历等。综上所述本设计具有设计方便、功能多样、电路简洁成本低廉等优点,符合社会发展的趋势,前景广阔。

目录

1 绪论 1

1.1电子钟的发展 1

1.2 FPGA简介 1

1.3 VHDL语言简介 2

2 设计方案 3

2.1设计要求 3

2.2设计实现功能 3

2.3模块设计 4

2.3.1计时模块 4

2.3.2分计数器 6

2.3.3时计数 7

2.3.4设置时间模块 7

2.3.5整点报时模块 10

2.3.6显示时间模块 11

2.3.7控制数码管 12

2.3.8数码管显示器 14

2.3.9分频模块 15

2.3.10闹钟模块 17

3 系统设计 17

3.1 数字钟系统模块框图 18

4 硬件设计 18

4.1 电源接口电路设计 18

4.2 电源系统设计 18

4.3 JTAG端口和FPGA配置电路设计 19

4.4 数码管电源扩展电路 19

4.5 数码管电路 19

4.6 指示灯显示电路 19

结 论 20

致 谢 21

参 考 文 献 22

附录.23

1 绪论 随着EDA技术的发展和应用领域的扩大与深入,EDA技术在电子信息、通信、自动控制及计算机应用领域的重要性日益突出。EDA技术就是依赖功能强大的计算机,在 EDA工具软件平台上,对以硬件描述语言VHDL为系统逻辑描述手段完成的设计文件,自动地完成逻辑优化和仿真测试,直至实现既定的电子线路系统功能。近十年来随着超大规模集成电路和软件技术的快速发展,使数字系统集成到一片集成电路内成为可能,许多公司都推出了非常好的CPLD 和FPGA 产品,并为这些产品的设计配备了设计、下载软件,这些软件除了支持图形方式设计数字系统外,还支持设计许多种数字系统的设计语言,使数字系统设计起来更加容易,可以说数字电子技术的设计进入了一个新时代。在这样一个大背景下,熟练掌握相关功能模块的开发就成为设计者必备的一部分知识。

1.1电子钟的发展 钟表的数字化给人们生产生活带来了极大的方便,而且大大地扩展了钟表原先的报时功能,诸如定时自动报警、按时自动打铃、时间程序自动控制、定时广播、定时启闭路灯等。所有这些,都是以钟表数字化为基础的。因此,研究电子万年历及扩大其应用,有非常现实的意义。数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更长的使用寿命,因此得到了广泛的使用。电子万年历从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。 因此,我们此次设计与制作电子万年历就是为了了解数字钟的原理,从而学会制作数字钟。而且通过万年历的制作进一步了解各种在制作中用到的中小规模集成电路的作用及使用方法,且由于电子万年历包括组合逻辑电路和时序电路,通过它可以进一步学习与掌握各种组合逻辑电路与时序电路的原理与使用方法。 1.2 FPGA简介 FPGA是现场可编程门阵列(Field programmable gates array)的英文简称。是有可编程逻辑模块组成的数字集成电路(IC)。这些逻辑模块之间用可配置的互联资源。设计者可以对这些器件进行编程来完成各种各样的任务。 PLD/FPGA是近几年集成电路中发展最快的产品。由于PLD性能的高速发展以及设计人员自身能力的提高,可编程逻辑器件供应商将进一步扩大可编程芯片的领地,将复杂的专用芯片挤向高端和超复杂应用。据IC Insights的数据显示,PLD市场从1999年的29亿美元增长到去年的56亿美元,几乎翻了一番。Matas预计这种高速增长局面以后很难出现,但可编程逻辑器件依然是集成电路中最具活力和前途的产业。 复杂可编程逻辑器件。 可编程逻辑器件的两种主要类型是现场可编程门阵列(FPGA)和复杂可编程逻辑(CPLD)。 在这两类可编程逻辑器件中,FPGA提供了最高的逻辑密度、最丰富的特性和最高的性能。 现在最新的FPGA器件,如Xilinx Virtex"系列中的部分器件,可提供八百万"系统门"(相对逻辑密度)。 这些先进的器件还提供诸如内建的硬连线处理器(如IBM Power PC)、大容量存储器、时钟管理系统等特性,并支持多种最新的超快速器件至器件(device-to-device)信号技术。 FPGA被应用于范围广泛的应用中,从数据处理和存储,以及到仪器仪表、电信和数字信号处理等。 1.3 VHDL语言简介 VHDL :vhsic(very high speed integrated circuit)hardware descriptiong language,也就是超高速集成电路硬件描述语言,vhdl语言是一种用于电路设计的高级语言。它在80年代的后期出现。最初是由美国国防部开发出来供美军用来提高设计的可靠性和缩减开发周期的一种使用范围较小的设计语言。但是,由于它在一定程度上满足了当时的设计需求,于是他在1987年成为ansi/ieee的标准(ieee std 1076-1987)。1993年更进一步修订,变得更加完备,成为ansi/ieee的ansi/ieee std 1076-1993标准。目前,大多数的cad厂商出品的eda软件都兼容了这种标准。它的应用主要是应用在数字电路的设计中。目前,它在中国的应用多数是fpga/cpld/epld的设计中。当然在一些实力较为雄厚的单位,它也被用来设计asic。 VHDL主要用于描述数字系统的结构,行为,功能和接口。除了含有许多具有硬件特征的语句外,VHDL的语言形式、描述风格以及语法是十分类似于一般的计算机高级语言。VHDL的程序结构特点是将一项工程设计,或称设计实体(可以是一个元件,一个电路模块或一个系统)分成外部(或称可视部分,及端口)和内部(或称不可视部分),既涉及实体的内部功能和算法完成部分。在对一个设计实体定义了外部界面后,一旦其内部开发完成后,其他的设计就可以直接调用这个实体。这种将设计实体分成内外部分的概念是VHDL系统设计的基本点。与其他的硬件描述语言相比,VHDL具有更强的行为描述能力。从而决定了他成为系统设计领域最佳的硬件描述语言。强大的行为描述能力是避开具体的器件结构,从逻辑行为上描述和设计大规模电子系统的重要保证。 VHDL丰富的仿真语句和库函数,使得在任何大系统的设计早期就能查验设计系统的功能可行性,随时可对设计进行仿真模拟。VHDL语句的行为描述能力和程序结构决定了他具有支持大规模设计的分解和已有设计的再利用功能。符合市场需求的大规模系统高效,高速的完成必须有多人甚至多个开发组共同并行工作才能实现。对于用VHDL完成的一个确定的设计,可以利用EDA工具进行逻辑综合和优化,并自动的把VHDL描述设计转变成门级网表。VHDL对设计的描述具有相对独立性,设计者可以不懂硬件的结构,也不必管理最终设计实现的目标器件是什么,而进行独立的设计。 2 设计方案2.1设计要求 2.2设计实现功能该数字电子钟能够实现时、分、秒计时功能;校准时和分的功能;校准时间时秒清零的功能;整点报时的功能; 2.3模块设计

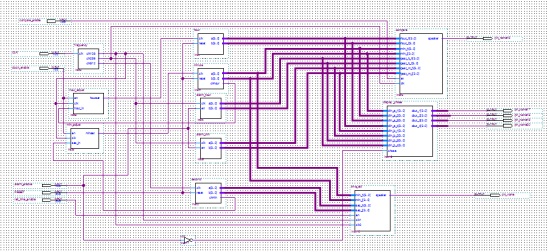

图1.模块总设计图 2.3.1计时模块 秒计数是由一个六十进制的计数器构成,生成元器件如下

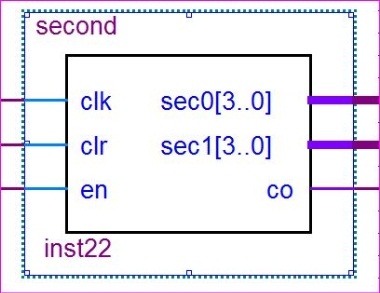

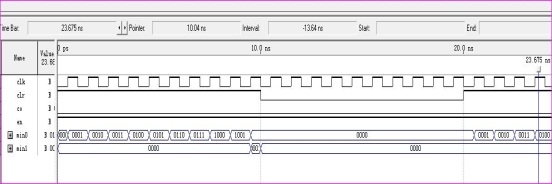

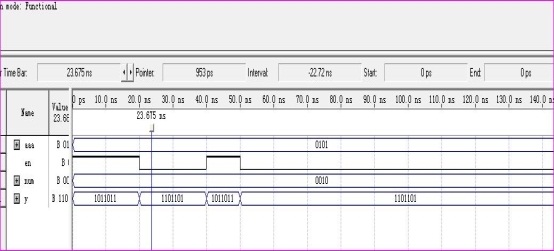

图2 Clk:驱动秒计时器的时钟信号Clr:校准时间时清零的输入端En:使能端Sec0[3..0] sec1[3..0]:秒的高位显示,低位显示Co:进位输出端,作为分的clk输入 仿真图如下:

图3

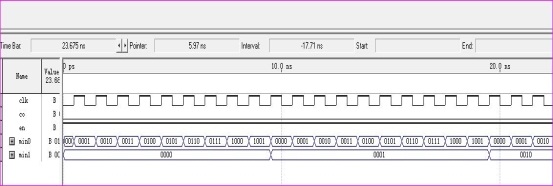

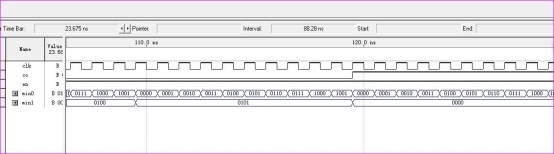

图4 2.3.2分计数器分计数器是由六十进制的计数器构成,生成元器件如下

图5 Clk:设置分输入和秒进位的或输入 En:使能输入 Min1[3..0] min0[3..0]:分的高位显示,低位显示 Co:向时的进位输出仿真图如下:

图6 2.3.3时计数 时计数器是由二十四进制的计数器构成,生成元器件如下

图7 Clk:设置时间输入和分进位输入的或en:使能端h1[3..0] h0[3..0]:时的高位显示和低位显示仿真图如下:

图8 2.3.4设置时间模块 按键去抖动,生成元器件如下

图9 Clk:256hz频率输入Reset:接GNDDin:接按键Dout:输出传给按键选择器仿真图如下:

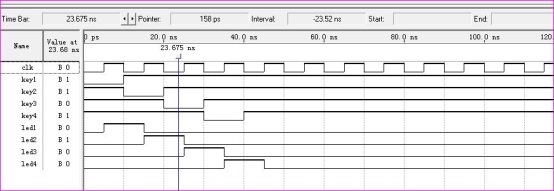

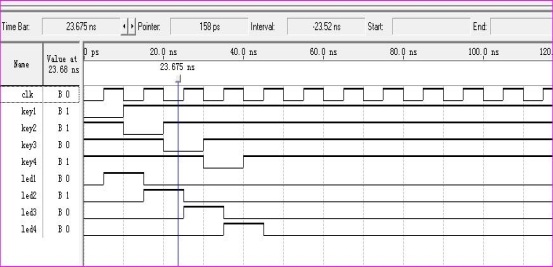

图10 按键选择器,生成元器件如下

图11 Clk:16hz输入Key1:按键调分的输入Key2:按键调时的输入Key3:按键秒清零的输入Led1:输出信号给分元器件Led2:输出信号给时元器件Led3:输出清零信号给秒元器件仿真图如下:

图12 2.3.5整点报时模块

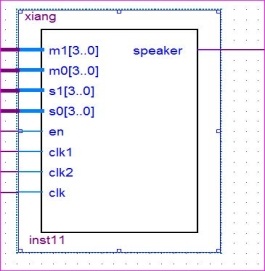

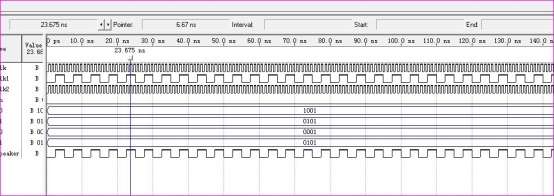

图13 Clk1:接512hzClk2 clk:En:使能输入M1[3..0] m0[3..0]:接分的高位输出和低位输出S1[3..0] s0[3..0]:接秒的高位输出和低位输出Speaker:连接蜂鸣器仿真图如下:

图14 2.3.6显示时间模块 模八的器件控制八个数码管显示的循环,生成元器件如下

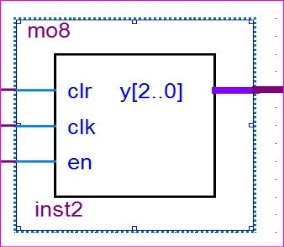

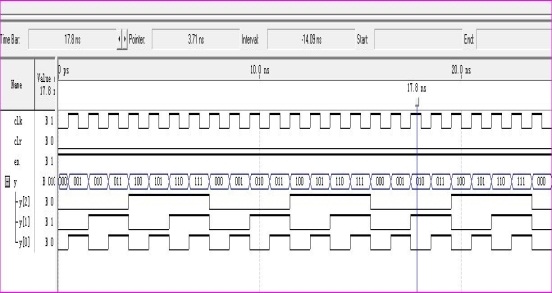

图15 Clk:输入

Clr:接GND

En:使能端

Y[2..0]:输出接数码管三个接受端

仿真图如下:

图16 2.3.7控制数码管八选一的器件控制数码管的亮或不亮,生成元器件如下

图17 Sel【2..0】:连接模八器件M7[3..0] m6[3..0]:连接秒的高位和低位输出M5[3..0]:接vcc(显示横)M4[3..0] m3[3..0]:接分的高位和低位输出M2[3..0]:接vcc(显示横)M1[3..0] m0[3..0]:连接时的高位低位输出Y[3..0]:输出给数码管显示

仿真图如下:

图18

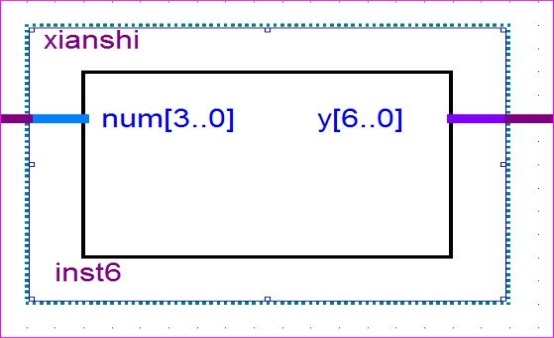

2.3.8数码管显示器 数码管显示器件,生成元器件如下

图19 Num[3..0]:接收八选一的输出信号Y[6..0]:驱动数码管显示

仿真图如下:

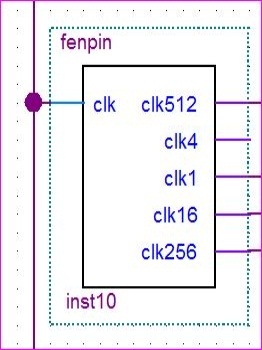

图20 2.3.9分频模块 分频器生成的元器件如下:

图21 Clk:时钟输入

Clk512:512hz给响铃模块

Clk1:1hz输出给秒计数器

Clk16:16hz输出给按键选择器

Clk256:256hz输出给按键抖动

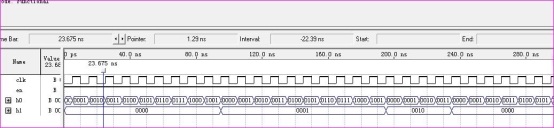

仿真图如下:

图22 2.3.10闹钟模块 比较器,比较当时显示时间与设置的闹钟时间是否相等,如相等,输出信号给蜂鸣器。生成元器件如下:

图23 Clk clk1:使能输入

H0[3..0] h1[3..0]:闹钟设置时间的分输入

H3[3..0] h2[3..0]:闹钟设置时间的时输入

S0[3..0] s1[3..0]:现在时间的分的输入

S2[3..0] s3[3..0]:现在时间的时的输入

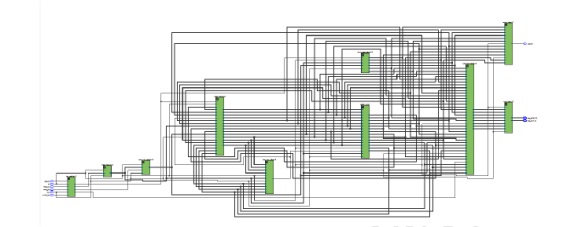

Y:输出信号给蜂鸣器3 系统设计 完成了数字钟各个模块的仿真验证工作后,接下来把模块有机地结合起来就构成了一个完整的数字钟。这里要完成的工作即是编写数字钟的顶层设计代码,将各个模块连接起来。 3.1 数字钟系统模块框图 用quartuse ii 对系统工程进行综合以后,点击RTL_VIWER系统可以自动生成设计的系统原理图(RTL视图)。

图3 4 硬件设计 前面我们的硬件描述语言已经把整个设计的做完,功能仿真也进行完毕了。但是我们的硬件设计的核心器件还没有定下来。采用器件(EP4CE6E22C8)对工程进行综合编译,可以看到资源占用报告。 4.1 电源接口电路设计 电源接口电路采用了两种供电的方式,满足不同的情况下使用。(1)Micro Usb供电,取电方便,用智能手机的充电线或者充电宝均可取电;(2)排针供电,但是必须要实验室直流电源通过排线接入5V电源。 电路中使用D1用来防反接,防止电源接反;R1使用的是自恢复保险丝,当后面电路意外短路的时,电阻急剧增大,形成高阻状态,防止烧坏后面电路的器件,当短路情况消失后,电阻减少,形成低阻状态,从而不需要人工干预,有效地保护电路LED作为一个电源指示灯,当电源接好并且K1开关打开时电源指示灯常亮。 4.2 电源系统设计 FPGA芯片需要用到3种电源供电,所以电路中设计3种电源转换电路 (1)5V电源转33V,E5、E6用来滤波储能,C3、C6用来滤出高频电源噪声 (2)5V电源转2.5V,外部加的滤波电容功能同上。 (3)3V电源转1.2V,外部的电容功能同上。 4.3 JTAG端口和FPGA配置电路设计 程序的下载,采用通用的JTAG方式下载程序,由于FPGA掉电易失,所以需要挂一个存储器。电路中用的是EPCS16S18N,设计PCB板的时候需要注意的地方,就是有些管脚需要上拉电阻。 4.4 数码管电源扩展电路 此次设计的数码管电路采用动态扫描的方式来显示。由于电路中有8个数码管,如果不采用动态扫描电路,那么将会用到60多个I/O口,不利用PCB布线且也浪费了FPGA芯片的I/O口。由于闪烁的频率在大于40HZ后,人眼就无法识别闪烁了,这样,在程序中设置每个数码管的点亮时间大于40HZ就会实现眼睛被欺骗的结果,数码管常亮。在使用数码管动态扫描电路的时候,一定要注意驱动电流的选择,如果不增加电流扩展电路,那么最终的结果就是数码管的显示很暗又或者显示不稳定,电路中每个公共信号都采用一个NPN三极管来扩展电流,增加驱动能力。 4.5 数码管电路 电路里面的使用了8个上图所示的数码管,采用共阴极的接法,程序中按照8个数码管从高到低位分时选择seg_en_x的管脚,点亮选择的数码管,由于分时选择的速度很快,远远大于人眼能够识别的频率,从而看上去数码管都是亮的。 4.6 指示灯显示电路 电路设计上留了4个不同颜色的灯,均通过FPGA芯片的IO口直接供电,高电平,点亮对应的灯,这4种灯具有以下的功能:LED3(闹钟设置模式指示灯)、LED4(日期设置模式指示灯)、LED5(时间调整模式指示灯)、LED6(正常显示模式下指示灯)。 结 论 通过这次课设实训,在硬件方面,使我们对EDA试验箱有了很多的了解,弥补了我们的知识的缺陷,同时对EDA试验箱内部的工作原理,以及EDA试验箱各个实验模式的功能很作用有了一定的了解,学习了硬件引脚绑定过程,以及绑定的一些基本常识,并动手完成了绑定,这样不仅拓宽我们的知识面,增强动手能力和实践能力,同时还培养我们的分析和解决实际问题的能力。

在软件方面,我们通过分组在软件Max+plus2上独立完成老师给我们的实训题目——电子钟。从开始分析点钟原理,在定义底层文件名称,编写底层文件程序,然后链接各个模块,到最终完成测试,并运行成功,这些加强了我们的分析问题的能力,提高了我们编程的能力,同时还培养了我们独立完成任务和查阅资料删选资料的能力,虽然完成的软件在实际运用中还有很多不足,比如软件运行的环境有限,程序的效率不高,在老师的要求上也不能全部到达预期的最好效果,等等一些问题,这都需要我们以后更深层次的加以修改,使其更加简单更加方便更加通俗易懂。

电子日历一路编来可谓是坎坎坷坷,但大家都没有放弃,积极主动的找老师、找同学帮忙解决难题。后来,又重新分析原理,重复操作,遇到困难马上向老师提问,及时解决问题,这样的效果很明显。

在这次实训中,我深深的感受到上课听讲的重要性,课设中遇到的很多问题都是老师上课讲解的一些难点,自己没有很好的领悟的地方。每个学生对老师课堂上讲的内容的接收都是不一样的,通过向老师请教,同学讨论,最后才得以解决问题,实训才能得以成功。

从整体看这次实训是很成功的,让我们都有很大的收获,同时也非常感谢在实训过程中给予我们很大帮助的老师,在老师耐心细心的指导下,我才能很好的完成实训认务。

附录

PCB图

原理图

- 代码

- /*=====================================================

- *****************************************************

- design name :wipe_key_shake

- use :按键消抖模块

- engineer :

- version :V0.1

- change note :

- V0.1 首次建立 :

- ****************************************************

-

- *****************************************************

- 功能说明:

-

- *****************************************************

-

- *****************************************************

- 端口信号说明:

- in clk :50M时钟输入

- in rst_n :复位信号输入

-

- in mode_key :模式按键输入

- in move_key :移位按键输入

- in add_key :数值加键输入

- in switch_key :显示选择按键输入

-

- out speaker :喇叭端口

-

- out seg_en :数码管使能端

- out seg_data :数码管数据端

- *****************************************************

- ========================================================*/

-

- module clock

- (

- input clk ,

- input rst_n ,

-

-

- input mode_key ,

- input move_key ,

- input add_key ,

- input switch_key ,

-

- output speaker ,

-

- output [7:0] seg_en ,

- output [6:0] seg_data //从高到低位abcdefg

- );

-

-

- //========================================================

- //*****************按键模块定义***************************

- wire filter_mode_key;

- wire filter_move_key;

- wire filter_add_key;

- wire filter_switch_key;

- //========================================================

-

-

- //========================================================

- //*****************模式设置模块定义***********************

- wire [1:0] mode;

- //========================================================

-

- //========================================================

- //*****************位置调整模块定义***********************

- wire [2:0] move_site;

- //========================================================

-

- //========================================================

- //*****************时钟运行模块定义***********************

- wire [3:0] second_u;

- wire [3:0] second_d;

- wire [3:0] minute_u;

- wire [3:0] minute_d;

-

- wire [3:0] hour_u;

- wire [3:0] hour_d;

-

- wire [3:0] date_u;

- wire [3:0] date_d;

- wire [3:0] month_u;

- wire [3:0] month_d;

- wire [3:0] year_u;

- wire [3:0] year_d;

- wire [3:0] year_h;

- wire [3:0] year_k;

- //========================================================

-

-

- //========================================================

- //*****************时间调整模块定义***********************

- wire [3:0] adjust_second_u;

- wire [3:0] adjust_second_d;

- wire [3:0] adjust_minute_u;

- wire [3:0] adjust_minute_d;

- wire [3:0] adjust_hour_u;

- wire [3:0] adjust_hour_d;

-

- wire [3:0] adjust_date_u;

- wire [3:0] adjust_date_d;

- wire [3:0] adjust_month_u;

- wire [3:0] adjust_month_d;

- wire [3:0] adjust_year_u;

- wire [3:0] adjust_year_d;

- wire [3:0] adjust_year_h;

- wire [3:0] adjust_year_k;

- //========================================================

-

- //========================================================

- //*****************闹钟调整模块定义***********************

- wire [3:0] alarm_second_u;

- wire [3:0] alarm_second_d;

- wire [3:0] alarm_minute_u;

-

- wire [3:0] alarm_minute_d;

- wire [3:0] alarm_hour_u;

- wire [3:0] alarm_hour_d;

- //========================================================

-

- //========================================================

- //*****************闹钟判断模块定义***********************

- //无

- //========================================================

-

- //========================================================

- //*****************闰年判断模块定义**********************

- wire leap_year_en;

- //========================================================

-

- //========================================================

- //*****************数码管数值选择模块定义*****************

- wire [3:0] num8;

- wire [3:0] num7;

- wire [3:0] num6;

- wire [3:0] num5;

- wire [3:0] num4;

- wire [3:0] num3;

- wire [3:0] num2;

- wire [3:0] num1;

- //========================================================

-

- //========================================================

- //*****************数码管译码与动态扫描模块定义***********

- //无

- //========================================================

-

-

-

- //========================================================

- //*****************按键模块例化***************************

- key_module U1

- (

-

- .clk (clk ),

- .rst_n (rst_n ),

-

- .mode_key (mode_key ),

- .move_key (move_key ),

- .add_key (add_key ),

- .switch_key (switch_key ),

-

- .filter_mode_key (filter_mode_key ),

- .filter_move_key (filter_move_key ),

- .filter_add_key (filter_add_key ),

- .filter_switch_key (filter_switch_key)

- );

- //========================================================

-

-

- //========================================================

- //*****************模式设置模块例化***********************

- mode_module U2

- (

- .clk (clk ),

- .rst_n (rst_n ),

-

- .mode_key (filter_mode_key),

- .mode (mode )

- );

- //========================================================

-

-

- //========================================================

- //*****************位置调整模块例化***********************

- move_site_module U3

- (

- .clk (clk ),

- .rst_n (rst_n ),

-

- .mode (mode ),

- .move_key (filter_move_key),

-

-

- .move_site (move_site )

- );

-

- //========================================================

-

-

- //========================================================

- //*****************时钟运行模块例化***********************

- clock_run U4

- (

- .clk (clk ),

- .rst_n (rst_n ),

-

- .mode (mode ),

- .leap_year_en (leap_year_en ),

-

- .adjust_second_u (adjust_second_u),

- .adjust_second_d (adjust_second_d),

- .adjust_minute_u (adjust_minute_u),

- .adjust_minute_d (adjust_minute_d),

- .adjust_hour_u (adjust_hour_u ),

- .adjust_hour_d (adjust_hour_d ),

-

- .adjust_date_u (adjust_date_u ),

- .adjust_date_d (adjust_date_d ),

- .adjust_month_u (adjust_month_u ),

- .adjust_month_d (adjust_month_d ),

- .adjust_year_u (adjust_year_u ),

- .adjust_year_d (adjust_year_d ),

- .adjust_year_h (adjust_year_h ),

- .adjust_year_k (adjust_year_k ),

-

- .second_u (second_u ),

- .second_d (second_d ),

- .minute_u (minute_u ),

- .minute_d (minute_d ),

- .hour_u (hour_u ),

-

- .hour_d (hour_d ),

-

- .date_u (date_u ),

- .date_d (date_d ),

- .month_u (month_u ),

- .month_d (month_d ),

- .year_u (year_u ),

- .year_d (year_d ),

- .year_h (year_h ),

- .year_k (year_k )

- );

- //========================================================

-

-

- //========================================================

- //*****************时间调整模块例化***********************

- clock_adjust U5

- (

- .clk (clk ),

- .rst_n (rst_n ),

-

- .mode (mode ),

- .move_site (move_site ),

- .leap_year_en (leap_year_en ),

- .add_key (filter_add_key ),

-

- .second_u (second_u ),

- .second_d (second_d ),

- .minute_u (minute_u ),

- .minute_d (minute_d ),

- .hour_u (hour_u ),

- .hour_d (hour_d ),

-

- .date_u (date_u ),

- .date_d (date_d ),

- .month_u (month_u ),

- .month_d (month_d ),

- .year_u (year_u ),

-

- .year_d (year_d ),

- .year_h (year_h ),

- .year_k (year_k ),

-

- .adjust_second_u (adjust_second_u ),

- .adjust_second_d (adjust_second_d ),

- .adjust_minute_u (adjust_minute_u ),

- .adjust_minute_d (adjust_minute_d ),

- .adjust_hour_u (adjust_hour_u ),

- .adjust_hour_d (adjust_hour_d ),

-

- .adjust_date_u (adjust_date_u ),

- .adjust_date_d (adjust_date_d ),

- .adjust_month_u (adjust_month_u ),

- .adjust_month_d (adjust_month_d ),

- .adjust_year_u (adjust_year_u ),

- .adjust_year_d (adjust_year_d ),

- .adjust_year_h (adjust_year_h ),

- .adjust_year_k (adjust_year_k )

- );

-

- //========================================================

-

-

- //========================================================

- //*****************闹钟调整模块例化***********************

- alarm_clock_adjust U6

- (

- .clk (clk ),

- .rst_n (rst_n ),

-

- .mode (mode ),

- .move_site (move_site ),

-

- .add_key (filter_add_key),

-

- .alarm_second_u (alarm_second_u),

- .alarm_second_d (alarm_second_d),

-

- .alarm_minute_u (alarm_minute_u),

- .alarm_minute_d (alarm_minute_d),

- .alarm_hour_u (alarm_hour_u ),

- .alarm_hour_d (alarm_hour_d )

- );

- //========================================================

-

-

- //========================================================

- //*****************闹钟判断模块定义例化*******************

- alarm_judge U7

- (

- .clk (clk ),

- .rst_n (rst_n ),

-

- .second_u (second_u ),

- .second_d (second_d ),

- .minute_u (minute_u ),

- .minute_d (minute_d ),

- .hour_u (hour_u ),

- .hour_d (hour_d ),

-

- .alarm_second_u (alarm_second_u ),

- .alarm_second_d (alarm_second_d ),

- .alarm_minute_u (alarm_minute_u ),

- .alarm_minute_d (alarm_minute_d ),

- .alarm_hour_u (alarm_hour_u ),

- .alarm_hour_d (alarm_hour_d ),

-

- .speaker (speaker )

-

- );

- //========================================================

-

-

- //========================================================

- //*****************闰年判断模块块例化*********************

-

-

- leap_year_judge U8

- (

- .clk (clk ),

- .rst_n (rst_n ),

-

- .mode (mode ),

-

- .year_u (year_u ),

- .year_d (year_d ),

- .year_h (year_h ),

- .year_k (year_k ),

-

- .adjust_year_u (adjust_year_u),

- .adjust_year_d (adjust_year_d),

- .adjust_year_h (adjust_year_h),

- .adjust_year_k (adjust_year_k),

-

- .leap_year_en (leap_year_en )

- );

-

- //========================================================

-

-

- //========================================================

- //*****************数码管数值选择模块例化*****************

- tube_num_select U9

- (

- .clk (clk ),

- .rst_n (rst_n ),

-

- .switch_key (filter_switch_key),

-

-

- .mode (mode ),

- .move_site (move_site ),

-

- .second_u (second_u ),

- .second_d (second_d ),

-

- .minute_u (minute_u ),

- .minute_d (minute_d ),

- .hour_u (hour_u ),

- .hour_d (hour_d ),

-

- .date_u (date_u ),

- .date_d (date_d ),

- .month_u (month_u ),

- .month_d (month_d ),

- .year_u (year_u ),

- .year_d (year_d ),

- .year_h (year_h ),

- .year_k (year_k ),

-

- .adjust_second_u (adjust_second_u ),

- .adjust_second_d (adjust_second_d ),

- .adjust_minute_u (adjust_minute_u ),

- .adjust_minute_d (adjust_minute_d ),

- .adjust_hour_u (adjust_hour_u ),

- .adjust_hour_d (adjust_hour_d ),

-

- .adjust_date_u (adjust_date_u ),

- .adjust_date_d (adjust_date_d ),

- .adjust_month_u (adjust_month_u ),

- .adjust_month_d (adjust_month_d ),

- .adjust_year_u (adjust_year_u ),

- .adjust_year_d (adjust_year_d ),

- .adjust_year_h (adjust_year_h ),

- .adjust_year_k (adjust_year_k ),

-

- .alarm_second_u (alarm_second_u ),

- .alarm_second_d (alarm_second_d ),

- .alarm_minute_u (alarm_minute_u ),

- .alarm_minute_d (alarm_minute_d ),

- .alarm_hour_u (alarm_hour_u ),

- .alarm_hour_d (alarm_hour_d ),

-

- .num8 (num8 ),

-

- .num7 (num7 ),

- .num6 (num6 ),

- .num5 (num5 ),

- .num4 (num4 ),

- .num3 (num3 ),

- .num2 (num2 ),

- .num1 (num1 )

- );

-

- //========================================================

-

- //========================================================

- //*****************数码管译码与动态扫描模块例化***********

- nixie_tube U10

-

- (

- .clk (clk ),

- .rst_n (rst_n ),

-

- .num8 (num8 ),

- .num7 (num7 ),

- .num6 (num6 ),

- .num5 (num5 ),

- .num4 (num4 ),

- .num3 (num3 ),

- .num2 (num2 ),

- .num1 (num1 ),

- .seg_en (seg_en ),

- .seg_data (seg_data) //从高到低位abcdefg

-

- );

- //========================================================

-

-

- endmodule

|